DOWNLOADED BY WIZARD.Z@FOXMAIL.COM

DOWNLOADED BY WIZARD.Z@FOXMAIL.COM

# Computer and network organization

Maarten van Steen Vrije Universiteit, Amsterdam

Henk Sips Delft University of Technology University of Amsterdam

4004, 8008, 8086, 8088, 80286, 80386, 80586, Pentium are trademarks of Intel Corporation 68000 is a trademark of Motorola Corporation Ada is a trademark of the US Department of Defense Ada Joint Program Office IBM, 360 are trademarks of International Business Machines Corporation MS-DOS is a trademark of Microsoft Corporation PDP-11 is a trademark of Digital Equipment Corporation UNIX is a trademark of UNIX Systems Laboratories

To Mariëlle and Annet

DOWNLOADED BY WIZARD.Z@FOXMAIL.COM

# Contents

| Foreword |              |        |                                       | xiii   |

|----------|--------------|--------|---------------------------------------|--------|

| Preface  |              |        |                                       | XV     |

| 1        | Introduction |        | )n                                    | 1      |

| 1.       | 1.1          | To sta | rt with                               | 1      |

|          |              | 1.1.1  | The <i>what</i> versus the <i>how</i> | 1      |

|          |              | 1.1.2  | Architecture versus organization      | 2      |

|          | 1.2          | Comp   | outers                                | 2<br>3 |

|          |              | 1.2.1  | The essence of computing devices      | 3      |

|          |              | 1.2.2  | The concept of a multi-level machine  | 8      |

|          | 1.3          | -      |                                       | 14     |

|          |              | 1.3.1  | The demand for computer networks      | 14     |

|          |              | 1.3.2  | Some fundamental problems             | 16     |

|          |              | 1.3.3  | Expanding networks                    | 19     |

|          |              | 1.3.4  | Towards communication systems         | 23     |

|          | 1.4          | Furthe | er reading                            | 25     |

| 2        | On           | 27     |                                       |        |

|          | 2.1          | Introd | 27                                    |        |

|          | 2.2          |        |                                       | 28     |

|          |              |        | Numbers                               | 29     |

|          |              | 2.2.2  | Representing text                     | 36     |

|          | 2.3          | Opera  | itions                                | 38     |

|          |              | 2.3.1  | Boolean functions                     | 39     |

|          |              | 2.3.2  | Boolean algebra                       | 41     |

|          |              |        | Some examples                         | 43     |

|          |              | 2.3.4  | Towards the next step                 | 48     |

viii

|   | 2.4  | Digital circuits |                                          | 48  |

|---|------|------------------|------------------------------------------|-----|

|   |      | -                | Gates                                    | 49  |

|   |      | 2.4.2            | Implementing arbitrary Boolean functions | 52  |

|   |      |                  | Integrated circuits                      | 55  |

|   | 2.5  | Storin           | g data                                   | 60  |

|   |      | 2.5.1            | 1-bit memories                           | 60  |

|   |      | 2.5.2            | Storing bit strings                      | 65  |

|   |      | 2.5.3            | Large storage circuits                   | 68  |

|   | 2.6  | Summ             | ary and further reading                  | 72  |

| 3 | Con  | puters           |                                          | 77  |

|   | 3.1  | -                | computing                                | 77  |

|   |      |                  | Stepwise execution                       | 77  |

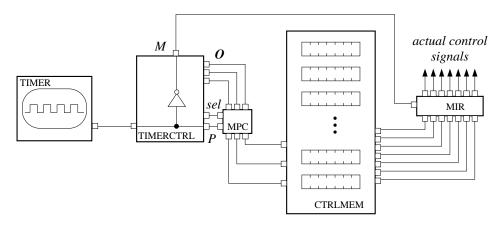

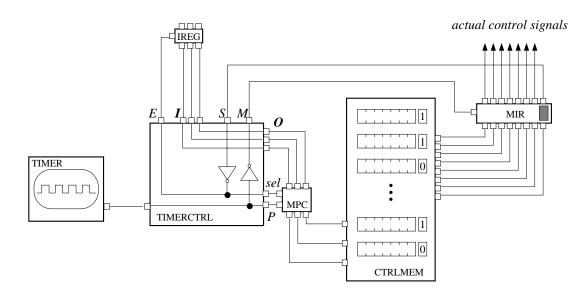

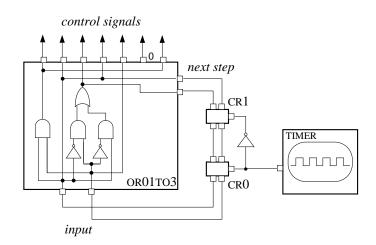

|   |      | 3.1.2            | Automated stepwise execution             | 82  |

|   |      |                  | Executing multiple microinstructions     | 86  |

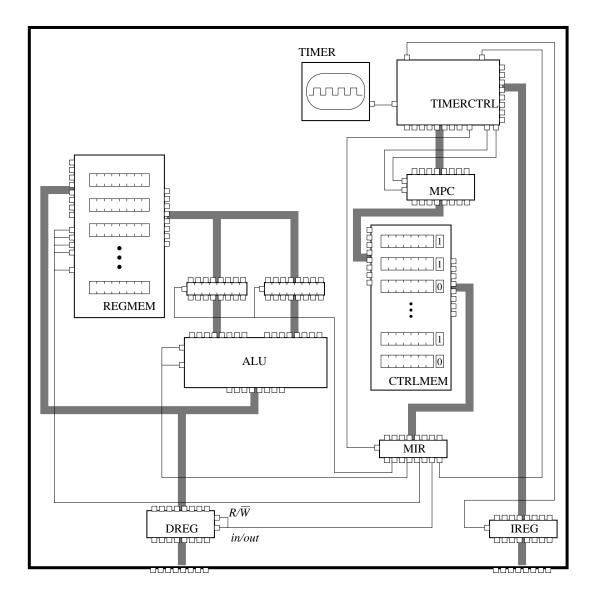

|   |      | 3.1.4            | A general architecture                   | 91  |

|   | 3.2  | Gener            | al processing                            | 93  |

|   |      | 3.2.1            | Instructions                             | 93  |

|   |      | 3.2.2            | Processors                               | 97  |

|   |      | 3.2.3            | On instruction sets                      | 101 |

|   | 3.3  | Interfa          | acing processors and memories            | 106 |

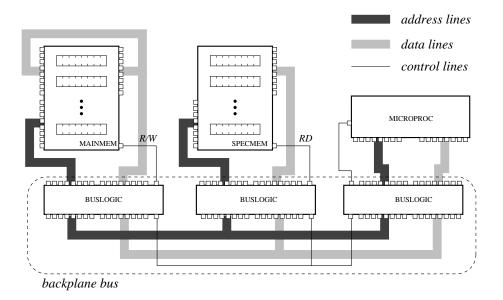

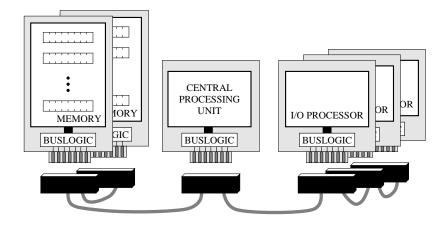

|   |      | 3.3.1            | General bus architectures                | 106 |

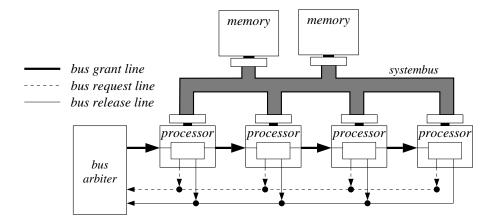

|   |      | 3.3.2            | Bus arbitration                          | 109 |

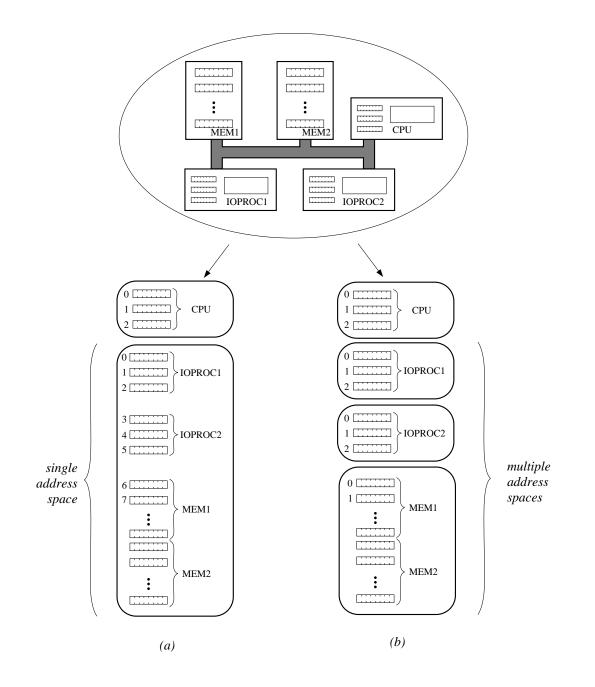

|   |      | 3.3.3            | Interprocessor communication             | 111 |

|   | 3.4  | Periph           | eral devices                             | 113 |

|   |      | 3.4.1            | Interfacing devices and processors       | 114 |

|   |      | 3.4.2            | Examples of peripheral devices           | 117 |

|   | 3.5  | Discus           | ssion and further reading                | 124 |

|   |      | 3.5.1            | Processor development                    | 124 |

|   |      | 3.5.2            | Processing power                         | 127 |

| 4 | From | n hard           | ware to software                         | 133 |

|   | 4.1  | Introd           | uction                                   | 133 |

|   |      | 4.1.1            | Towards software solutions               | 133 |

|   |      | 4.1.2            | Expressing programs                      | 134 |

|   |      | 4.1.3            | Executing programs                       | 136 |

|   | 4.2  |                  | nitive machine language                  | 137 |

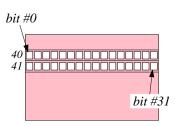

|   |      | 4.2.1            | A basic PRIMAL instruction set           | 138 |

|   |      | 4.2.2            | Subroutines in PRIMAL                    | 145 |

|   |      | 4.2.3            | Discussion                               | 150 |

|   | 4.3  | A stru           | ctured programming language              | 150 |

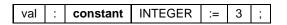

|   |      | 4.3.1            | Data types and variables                 | 151 |

|   |      | 4.3.2            | Statements                               | 156 |

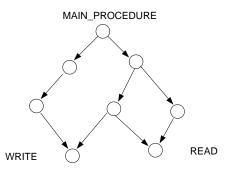

|   |      | 4.3.3            | Procedures                               | 160 |

|   |     | 4.3.4                     | Packages                                          | 166 |

|---|-----|---------------------------|---------------------------------------------------|-----|

|   | 4.4 | A BASAL virtual processor |                                                   | 172 |

|   |     | 4.4.1                     | The principle of a virtual processor              | 172 |

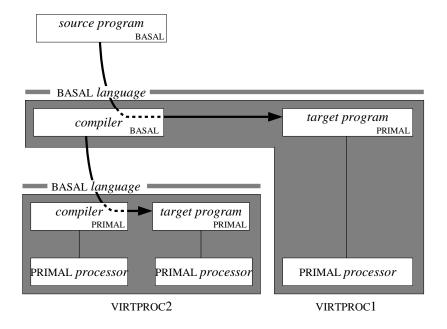

|   |     | 4.4.2                     | On automated translation                          | 175 |

|   | 4.5 | Towar                     | rds an extensible BASAL computer                  | 182 |

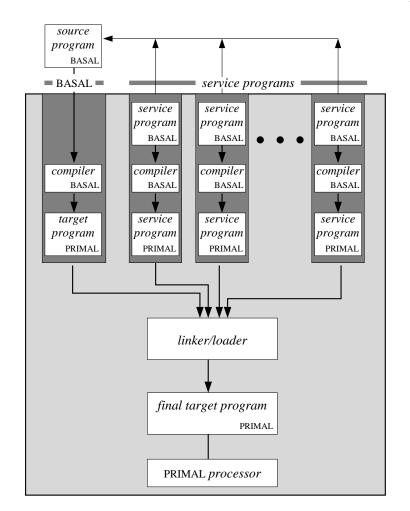

|   |     | 4.5.1                     | Controlling the translation process               | 182 |

|   |     | 4.5.2                     | Virtual devices                                   | 188 |

|   |     | 4.5.3                     | Linking and loading                               | 189 |

|   | 4.6 | Discu                     | ssion and further reading                         | 192 |

|   |     | 4.6.1                     | Machine languages                                 | 192 |

|   |     | 4.6.2                     | High-level languages                              | 194 |

|   |     | 4.6.3                     | Compiler technology                               | 197 |

| 5 | Ope | rating                    | systems                                           | 201 |

|   | 5.1 | Suppo                     | ort for multiple programs                         | 201 |

|   |     | 5.1.1                     | An example: disk I/O                              | 201 |

|   |     | 5.1.2                     | The problems                                      | 205 |

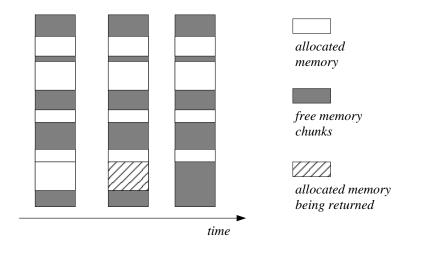

|   | 5.2 | Memo                      | bry management                                    | 207 |

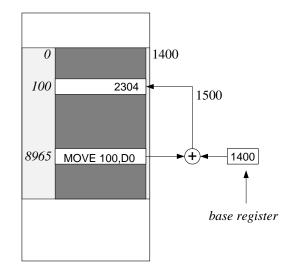

|   |     | 5.2.1                     | Program relocation                                | 207 |

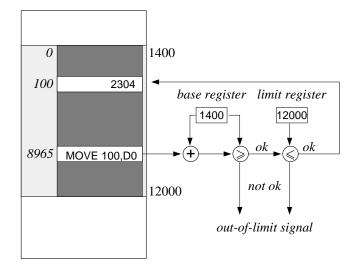

|   |     | 5.2.2                     | Procedure protection                              | 208 |

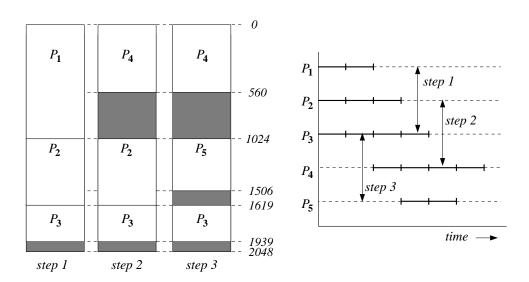

|   |     | 5.2.3                     | 5                                                 | 209 |

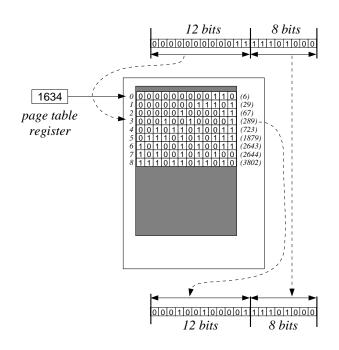

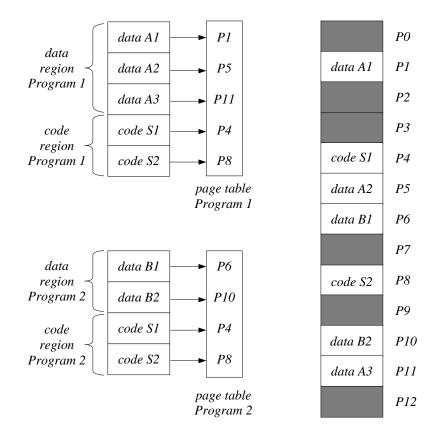

|   |     |                           | Advanced memory management: paging                | 212 |

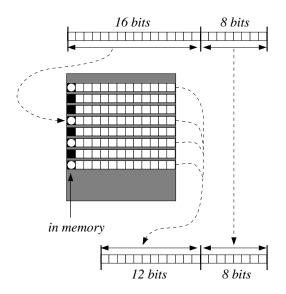

|   |     | 5.2.5                     | Advanced memory management: virtual memory        | 217 |

|   | 5.3 | Proces                    | ss management                                     | 219 |

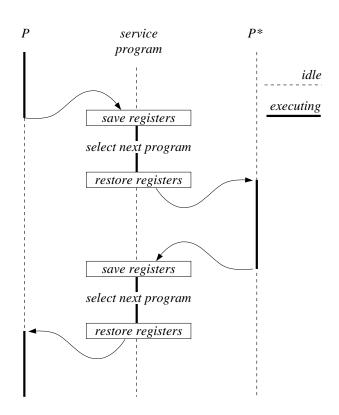

|   |     | 5.3.1                     | Context switching                                 | 220 |

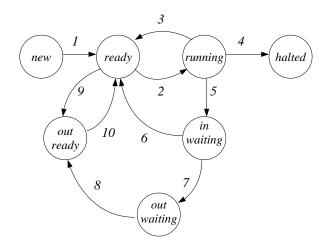

|   |     | 5.3.2                     | From processor contexts to processes              | 223 |

|   | 5.4 |                           | ss interference                                   | 228 |

|   |     | 5.4.1                     | Synchronization: semaphores                       | 229 |

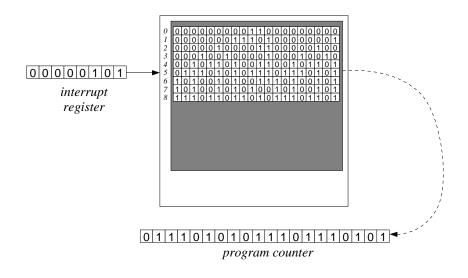

|   |     |                           | Interrupt handling                                | 234 |

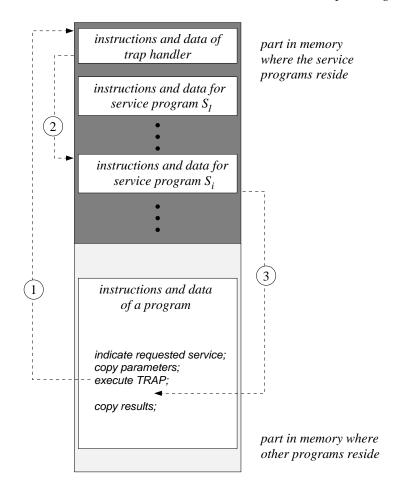

|   |     | 5.4.3                     | Forcing the use of service programs               | 236 |

|   | 5.5 | -                         | erating systems                                   | 239 |

|   |     | 5.5.1                     | 1 0 1                                             | 240 |

|   |     | 5.5.2                     | Architectural aspects of operating system kernels | 243 |

|   |     | 5.5.3                     | e                                                 | 247 |

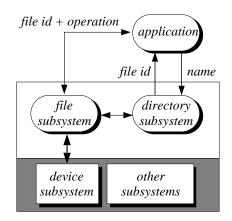

|   | 5.6 |                           | ample extension: file systems                     | 249 |

|   |     | 5.6.1                     | The concept of a file                             | 250 |

|   |     | 5.6.2                     | File implementation                               | 252 |

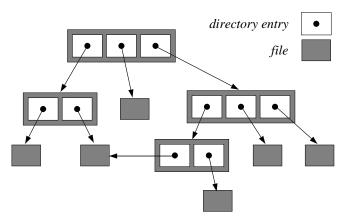

|   |     | 5.6.3                     | File organization: directories                    | 257 |

|   | 5.7 | Discus                    |                                                   | 259 |

|   |     | 5.7.1                     | Summary and further reading                       | 259 |

|   |     | 5.7.2                     | Operating systems today                           | 261 |

| 6 | Basi | c comr                               | nunication models                           | 265 |

|---|------|--------------------------------------|---------------------------------------------|-----|

|   | 6.1  | Descr                                | 265                                         |     |

|   |      | 6.1.1                                | Introduction                                | 265 |

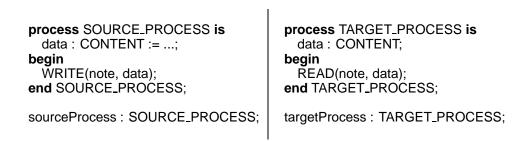

|   |      | 6.1.2                                | Processes in BASAL                          | 266 |

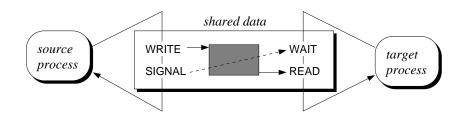

|   | 6.2  | Makir                                | ng use of shared data                       | 268 |

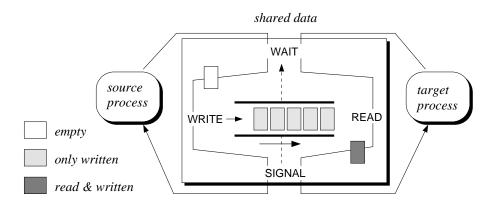

|   |      | 6.2.1                                | Handing over notes                          | 268 |

|   |      | 6.2.2                                | Shared streams for continuous communication | 271 |

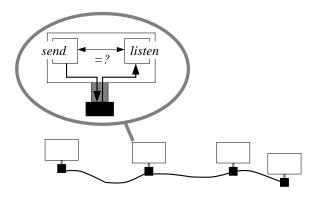

|   | 6.3  | Basic message-passing                |                                             | 280 |

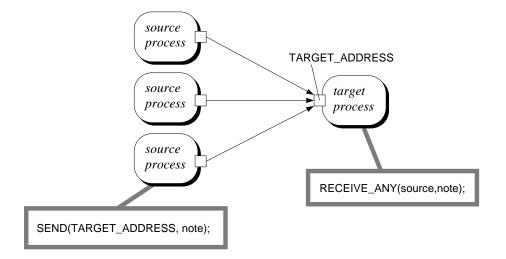

|   |      | 6.3.1                                | The basic model                             | 281 |

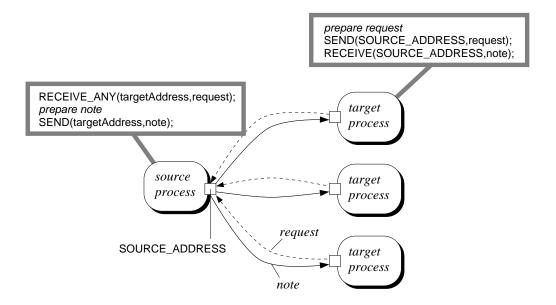

|   |      | 6.3.2                                | Passing notes revisited                     | 283 |

|   |      | 6.3.3                                | Semantics of message-based communication    | 287 |

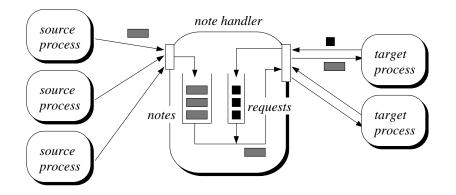

|   | 6.4  | Advanced message-based communication |                                             | 293 |

|   |      | 6.4.1                                | Channels                                    | 294 |

|   |      | 6.4.2                                | The rendez-vous and remote procedure call   | 303 |

|   |      | 6.4.3                                | Group communication                         | 307 |

|   | 6.5  | Discu                                | ssion and further reading                   | 310 |

|   |      | 6.5.1                                | Communication models                        | 310 |

|   |      | 6.5.2                                | Advanced communication models               | 313 |

| 7 | Con  | necting                              | g computers                                 | 317 |

|   | 7.1  | Introd                               | luction                                     | 317 |

|   | 7.2  | On wi                                | iring                                       | 318 |

|   |      | 7.2.1                                | Transmitting signals                        | 318 |

|   |      | 7.2.2                                | Receiving signals                           | 323 |

|   |      | 7.2.3                                | In the event of errors                      | 325 |

|   |      | 7.2.4                                | Making networks                             | 331 |

|   | 7.3  | Frame                                | e transmission                              | 336 |

|   |      | 7.3.1                                | Flow control                                | 337 |

|   |      | 7.3.2                                | Error control                               | 342 |

|   | 7.4  | Multi                                | plexing                                     | 348 |

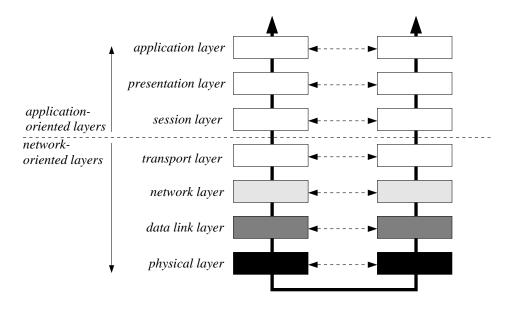

|   | 7.5  | Towa                                 | rds a layered approach                      | 351 |

|   |      | 7.5.1                                | Review of basic communication properties    | 351 |

|   |      | 7.5.2                                | The ISO/OSI reference model                 | 353 |

|   | 7.6  | Furthe                               | er reading                                  | 355 |

| 8 | Loca | al area                              | networks                                    | 357 |

|   | 8.1  | Introd                               | luction                                     | 357 |

|   | 8.2  | Gettin                               | ng access to a broadcast channel            | 358 |

|   |      | 8.2.1                                | General problems with broadcast channels    | 359 |

|   |      | 8.2.2                                | Contention systems                          | 361 |

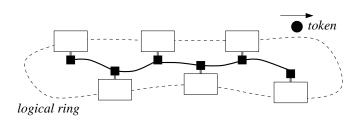

|   |      | 8.2.3                                | Collision-free systems                      | 364 |

|   |      | 8.2.4                                | On the performance of broadcast channels    | 372 |

|   | 8.3  | Interc                               | onnecting LANs                              | 375 |

|   |      | 8.3.1                                | Constructing large, high-speed networks     | 375 |

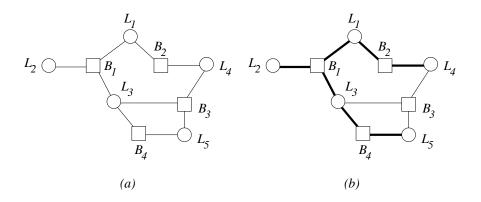

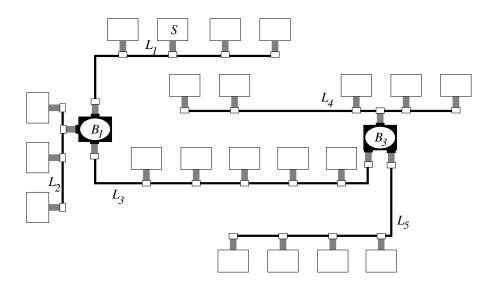

|                                         |      |          | Routing between LANs                    | 382 |

|-----------------------------------------|------|----------|-----------------------------------------|-----|

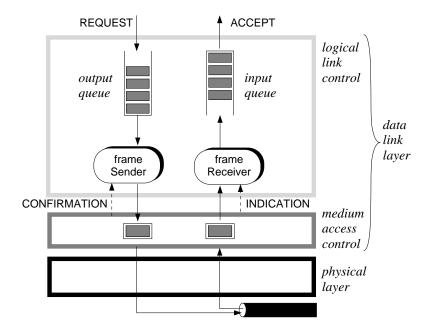

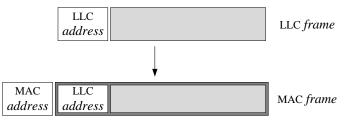

|                                         | 8.4  |          | network interfacing                     | 388 |

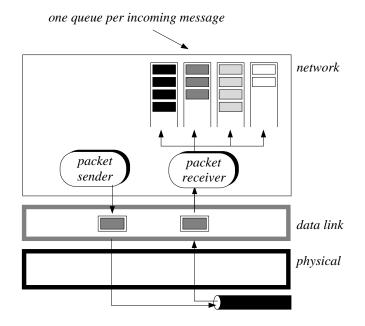

|                                         |      | 8.4.1    | Networks as peripheral devices          | 388 |

|                                         | ~ -  | 8.4.2    |                                         | 396 |

|                                         | 8.5  | -        | iter networks in software               | 398 |

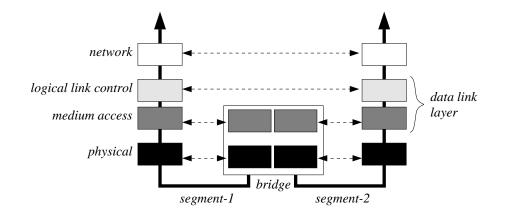

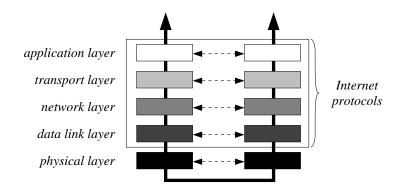

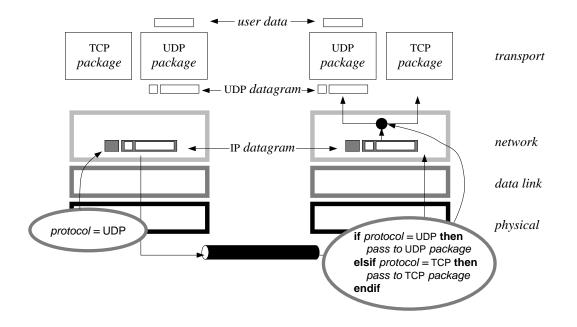

|                                         |      |          | Layering the network software           | 399 |

|                                         | _    | 8.5.2    | Supporting multiple protocols           | 405 |

|                                         | 8.6  | Discus   |                                         | 410 |

|                                         |      | 8.6.1    | Summary and further reading             | 410 |

|                                         |      | 8.6.2    | Improving local area networks           | 411 |

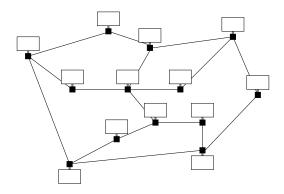

| 9                                       | Wide | e area n | etworks                                 | 415 |

|                                         | 9.1  | Expand   | ding communication systems              | 415 |

|                                         |      | 9.1.1    | Introduction                            | 415 |

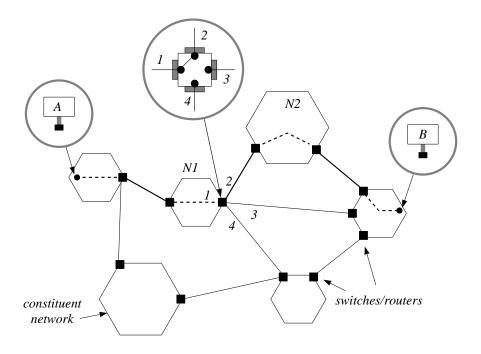

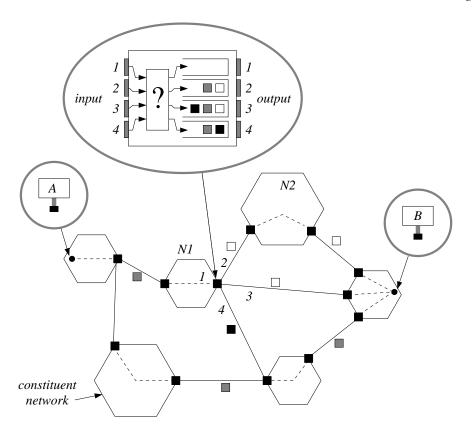

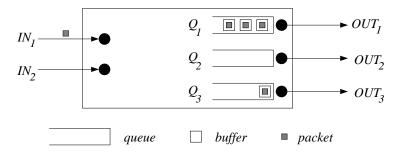

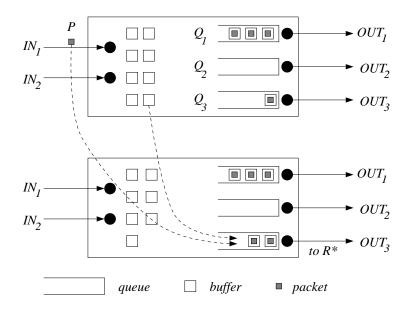

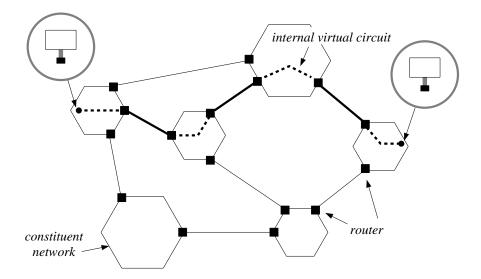

|                                         |      | 9.1.2    | Architectural features of WANs: routers | 416 |

|                                         |      | 9.1.3    | Building a worldwide network            | 418 |

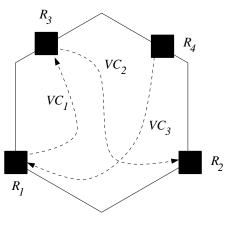

|                                         |      | 9.1.4    | Communication models revisited          | 422 |

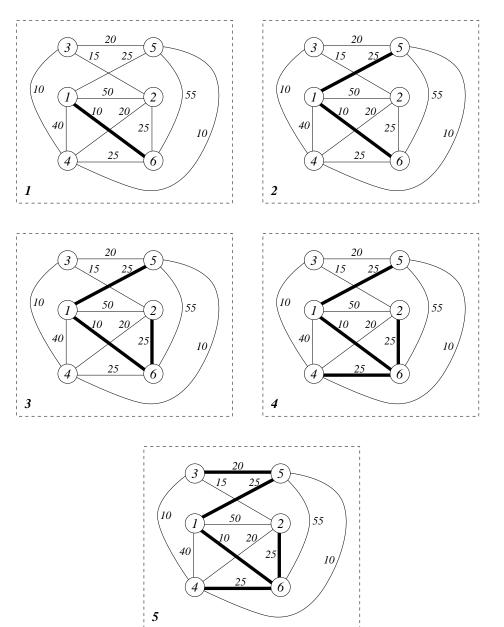

|                                         | 9.2  | Routin   | g in wide area networks                 | 425 |

|                                         |      | 9.2.1    | Network congestion                      | 426 |

|                                         |      | 9.2.2    | e                                       | 431 |

|                                         |      | 9.2.3    | Routing organization                    | 438 |

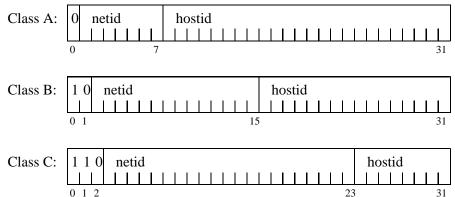

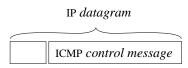

|                                         | 9.3  | Interne  | etworking                               | 441 |

|                                         |      | 9.3.1    | What makes internetworks different      | 441 |

|                                         |      | 9.3.2    | Internet packet fragmentation           | 444 |

|                                         |      | 9.3.3    | Modes of operation                      | 448 |

|                                         |      | 9.3.4    | An example: the Internet                | 451 |

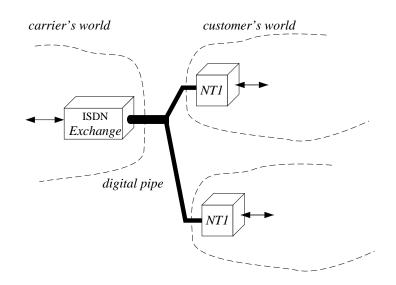

| 1 I I I I I I I I I I I I I I I I I I I |      | Integra  | ted services digital networks           | 460 |

|                                         |      | 9.4.1    | Introduction                            | 460 |

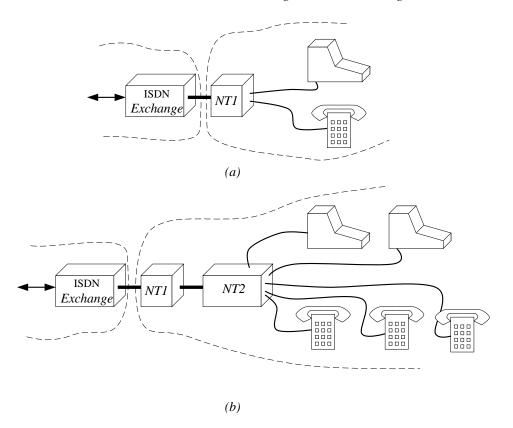

|                                         |      | 9.4.2    | ISDN architecture                       | 461 |

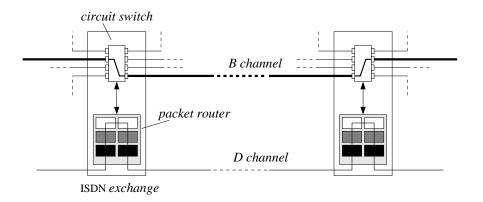

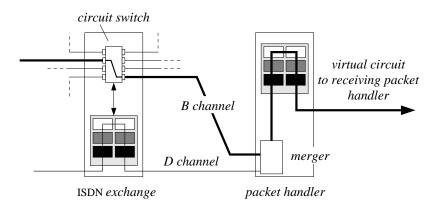

|                                         |      | 9.4.3    | ISDN communication support              | 464 |

|                                         |      | 9.4.4    | Broadband ISDN                          | 466 |

|                                         | 9.5  | Making   | g networks work                         | 469 |

|                                         |      | 9.5.1    | The transport layer                     | 469 |

|                                         |      | 9.5.2    | Error control                           | 472 |

|                                         |      | 9.5.3    | Flow control                            | 473 |

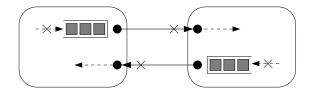

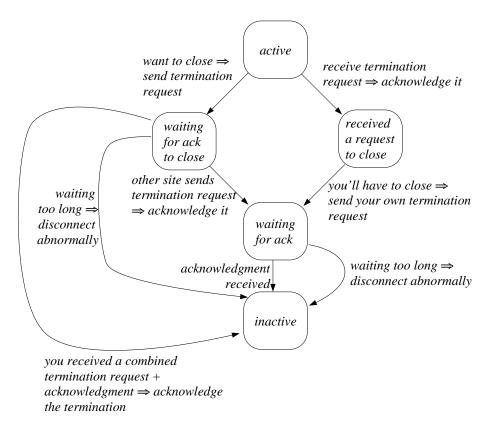

|                                         |      | 9.5.4    | Connection management                   | 474 |

|                                         | 9.6  | Summa    | ary and further reading                 | 477 |

|                                         |      | 9.6.1    | Wide area networks                      | 478 |

|                                         |      | 9.6.2    | Wide area digital networks              | 479 |

| 10                                      | Towa | ards co  | mmunication architectures               | 483 |

|                                         | 10.1 | From le  | ocal to global systems                  | 483 |

|                                         |      |          | The concept of distributed applications | 483 |

|                                         |      |          | Implicit assumptions made so far        | 486 |

# xii

| 10.2       | On open systems                           | 487    |

|------------|-------------------------------------------|--------|

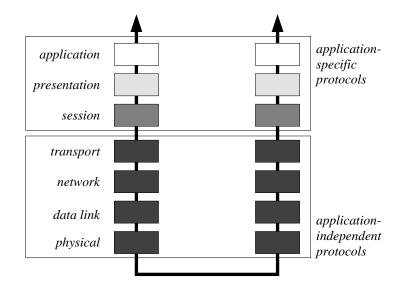

|            | 10.2.1 The OSI model completed            | 487    |

|            | 10.2.2 A simplified model for open system | ns 493 |

| 10.3       | Communication services                    | 495    |

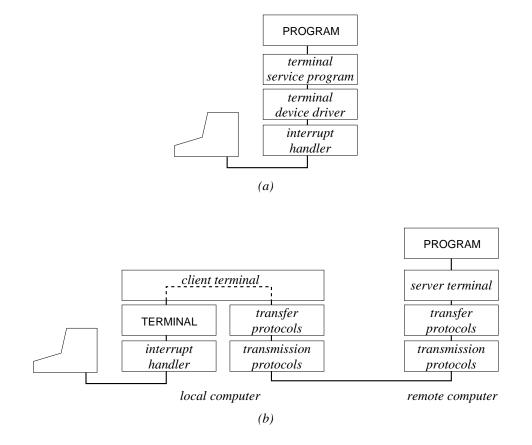

|            | 10.3.1 Terminal handling services         | 495    |

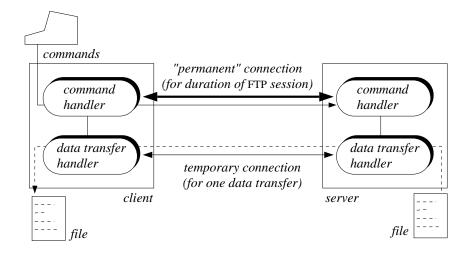

|            | 10.3.2 File handling services             | 500    |

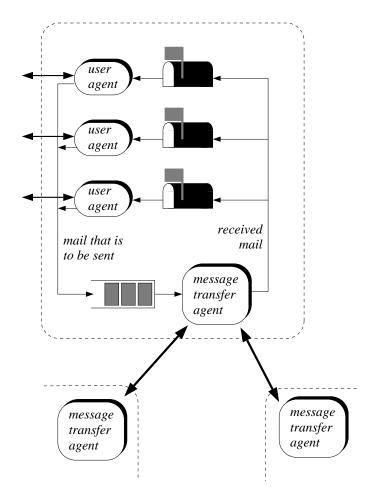

|            | 10.3.3 Message handling services          | 504    |

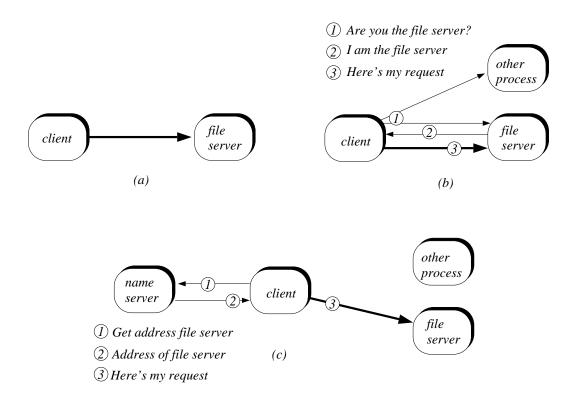

|            | 10.3.4 Name handling services             | 509    |

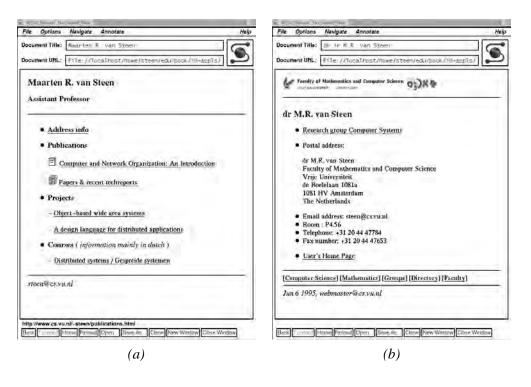

| 10.4       | The World Wide Web                        | 514    |

|            | 10.4.1 The Web's basic functionality      | 515    |

|            | 10.4.2 The underlying technology          | 515    |

| 10.5       | Discussion and further reading            | 517    |

|            | 10.5.1 On distributed applications        | 518    |

|            | 10.5.2 The communication layer            | 518    |

|            | 10.5.3 Wide area distributed applications | 520    |

| References |                                           | 523    |

| Index      | 532                                       |        |

# Foreword

This book solves the *Three Bears Problem*. As you may recall, when Goldilocks visited the three bears, some things were too big, and some things were too small, but she wanted something that was "just right."

Many scientists, engineers, and technical managers face the same problem. It is important for them to have a good grasp of modern computer technologies, including computer architecture, operating systems, and networks. All of these are complex and rapidly changing subjects.

Until now, these people have had two choices. On the one hand, there are many detailed computer science textbooks available for each subject separately. These books offer a comprehensive view of the subject, but require the reader to plow through 500–800 pages of material. Mastering computer architecture, operating systems, and networking might require absorbing 2000 pages of highly technical material.

On the other hand, bookstores are full of gee-whiz books telling how wonderful computers are and what they can do for you. Many are about specific systems, and are full of advice of the sort "To make X happen, click on icon Y." These books are written for readers with a casual interest in science and technology, but do not explain how computers and systems actually work inside.

For technically-oriented people in physics, chemistry, engineering, and management, neither of these choices is appropriate. What they need is a single volume that discusses the fundamentals of computer systems (architecture, operating systems, and networks) in considerable technical detail, but in a single well-integrated book. This is their book. In a little over 500 pages, it covers hardware, architecture, operating systems, communication, LANs, and WANs in a surprising amount of detail, with numerous algorithms given as actual programs in an Ada-like language.

At universities, this book can be used for a second computer course for non-computer science majors. It is also self contained, and makes fine reading for practicing professionals who want to keep up-to-date on three different subareas of computer science, but without having to read three different books. I recommend this book most highly for these audiences.

Andrew S. Tanenbaum

DOWNLOADED BY WIZARD.Z@FOXMAIL.COM

# Preface

# Why we have written this book

This book was written out of necessity. A few years ago, both of us were engaged in giving a course on the technical principles of computer systems for an audience with only a modest background in computer science. The goals set out for that course where quite challenging. First, undergraduate students were to be provided with a general insight into the actual working of computer systems, which covered the three main themes: computer organization, operating systems, and computer networks. Second, there was only room for 15 two-hour lectures, to be given in a single semester. Indeed, not an easy task to accomplish, especially when it turned out that hardly any single textbook existed that covered these three themes at an adequate introductory level.

The result was that an initial course text was written, comprising about 200 pages, which roughly explained the working of computer systems. The material was more or less equally divided between computer organization, operating systems, and computer networks. This course text, combined with the actual lectures given, proved at least one thing: explaining the technicalities of computer systems in a single semester was not only feasible, the students actually enjoyed it. Doing a complete rewrite and ending with a 550-page book is just one of those things that can happen when the two of us start having "good" ideas.

### The main questions that are addressed

As mentioned, in this book we have made an attempt to explain the working of computer systems, but in such a way that it should be possible to go through almost the entire material in just a single one-semester course. The book roughly addresses, in order, the following questions:

• What does a computer look like from the inside? In particular, we explain the essence of chips, processors, memory, peripheral devices such as hard disks and

#### xvi Preface

keyboards, and how these various components are connected to each other so that they can operate together.

- What is actually meant by a computer program? This question (which to some may seem so simple that they will have a hard time giving a right answer) is addressed in two ways. First, we explain how we can use a computer's so-called instruction set to develop programs. Second, we shall demonstrate that computer programs can be more easily written in a high-level programming language for which no real processor exists, but which can nevertheless be executed.

- What is an operating system, and how does it work? This is an important question as it addresses the way that modern computers appear to users. We will explain that an operating system is a special program that allows you to work conveniently and efficiently with a computer. Above all, we will emphasize the role of operating systems as a mechanism to abstract matters that are specific to hardware, and in particular that they provide an important means for communication by computers.

- How can computers be linked together? This is the first topic of computer networks. Our attention will initially focus on various hardware aspects, i.e. the physical appearance of computer networks. Also, we shall present the basics of how computer programs are to be constructed by which information between two or several computers can be exchanged. In a sense, the answer to this question is treated very much at the same level as the first question posed above.

- How does communication across a computer network take place? This is an important question that will also be addressed. We shall explain how messages can be transferred from one user to another, possibly crossing a network that spans the world, or alternatively, one that is used in conjunction with, for example, printers. Central to answering this question is the concept of communication protocols: what are they, and how are they realized?

These questions are not addressed in isolation. Instead, we follow an approach by which the working of computer systems is gradually exposed. This approach not only allows the reader to understand the essentials, but above all, will provide an *overall view* on the technical principles of computer systems.

A book such as this probably cannot do otherwise than present the essentials. And indeed, this is as far as we go. But in doing so, we have sought to provide an understanding of the subjects in such a way that the reader will see the big picture, but at the same time will have a feeling for the details that are involved. For example, we have found it important to explain *how* the interaction between hardware and software takes place, in particular when discussing operating systems. Strangely enough, this topic is often hardly discussed explicitly in books on either computer organization or operating systems. Likewise, we provide simplified examples of programs that illustrate how layering of software can be achieved. Layering is an important concept when explaining computer networks. We have been surprised by the fact that again only relatively few books explain how the concept can be made concrete. And although our approach only

permits us to give a glimpse of how layering works in practice, we feel that not doing this would have been a serious omission.

# **Intended readership**

With these things in mind, we have written our text for people that are somewhat familiar with computers. This means that we expect that the reader already has a basic feeling of what computers are, and what you can do with them. Having followed an introductory course in computer science will give an understanding of the material presented here. Most of all, it will make it much easier to comprehend concepts such as processors and programs, which are of vital importance to understanding computer systems. Having a reading knowledge of computer programs, for example written in Pascal, will help.

The material is, by its nature, technical. As such, undergraduate students in engineering disciplines and natural sciences will perhaps find the book easier to understand than others. However, we emphasize that the material has also been classroom tested for students in business information sciences. As we have said above, a basic interest in computer science as experienced during a first introductory course should be sufficient for a successful understanding of this book.

The book can also serve as an alternative for courses in computer organization, with less emphasis on architecture and more on modern subjects as concurrency and communication. To our opinion this change in material coverage will inevitably take place, since computers and communication will be increasingly integrated.

But apart from a being a textbook to be used as part of a course, the material is also intended for those who would wish to know more about the various general technical principles, but find existing textbooks simply too overwhelming to start with. In that case, this book may well form a good starting point, and may even be sufficient. If the latter is not the case, then enough knowledge and terminology will have been introduced to make the transition to more specialized textbooks.

We have made an attempt to organize the material in such a way that different types of readers will feel equally comfortable. First, we have included so-called elaboration sections, which are distinguished from the main text as follows:

▷ This is an example of an elaboration section, and can be skipped at first reading.

Elaboration sections often contain additional material that may be either too technical or too detailed to be discussed initially. In all cases, these sections may be skipped if so required: they do not interfere with the main text but are pure extensions of it.

Each chapter concludes with a summary or discussion, as well as references for further reading. Where explicitly noted, the reader is particularly encouraged to consult the referenced material as it will generally provide further insight into the material as we have presented it. Finally, each chapter, except the first one, has been augmented with a number of exercises. Starred exercises generally require reading the elaboration sections.

# More information

We find it important to keep the reader informed about additional material related to this book. Therefore, we have constructed a Web page at http://www.cs.vu.nl/~steen/cno.html. At present, the page contains links to problem solutions and Postscript versions of (nearly) all figures. Additional material will be made available through this Web page. You can also find out how and where we can be reached if you wish to contact us. Suggestions on how the book can be improved are most welcome, as well as any reports on errors and omissions.

# Acknowledgments

Writing a book is definitely something you cannot do without having the support from many others. In order to get this project started, it was necessary to install a UNIX-based support environment on a rather unwilling personal computer. Paul Kranenburg, Eelco van Asperen, and Reino de Boer helped to get the software where it was needed. Reino deserves special credit for additionally helping with many of the intricacies related to IATEX and TEX.

Others helped us get the manuscript right by reading portions of the material, and pointing out the sections that needed improvement. In this respect, we owe much to Theun Bruins, Leendert van Doorn, Jaap Gordijn, Tom Hoeksma, Philip Homburg, Mark Polman, Kees van Reeuwijk, Ron Roozendaal, Andy Tanenbaum, Louis Tinzelboer, Joachim Trescher, and Hans de Vreught. Special thanks go particularly to Marcel Beemster and Wim Stut who both managed to read the entire manuscript at a level of detail that often not only surprised us but above all proved to be invaluable.

But perhaps in the end, much of the support comes from those that will presumably never read the book, but who have nonetheless undergone the entire project from the very beginning. Mariëlle and Annet get all the credit for their support.

> Maarten van Steen Henk Sips

The field of computer and network organization is large, but an exciting one. The number of problems that have been tackled and are still being studied is so large that it is often difficult to obtain an overview of the subject without being swamped by all kinds of details. In order to avoid losing the way while studying the material in the chapters yet to follow, we start with giving some rough guidelines on what computer and network organization is mainly about. This introductory chapter is centered around Section 1.2 which outlines the essence of computers, and Section 1.3 in which we concentrate on computer networks.

# 1.1 To start with

In order to understand the material presented in this book it is necessary to look at problems of computer and network organization from the right perspective. Let's start by explaining how we plan to tackle the problems by telling what *our* perspective is.

# 1.1.1 The *what* versus the *how*

It is hard to imagine what our daily lives would be without having computers. We have become so familiar with their existence that they hardly surprise us any more. For example, we expect that much of the administration that we are confronted with is handled one way or the other by means of a computer. That the inventory of supermarkets is kept up to date by simply coupling the cash registers to the computer is something we tend to consider as normal. Using credit cards that are electronically processed is also something we are accustomed to. We have grown used to producing documents through advanced word processing systems rather than using typewriters. These are only a few examples. Computers have indeed simply become a fact of life.

But this is just one side of computers. To date, many people have a fairly good idea of *what* can be done with computers. But knowing *how* computer engineers attained their

remarkable achievements is a completely different story. As we have all become so acquainted with using computers, it also seems that we are willing to accept that it is necessary to be an expert to understand what's going on under the hood. And that is really unfortunate, for it is our belief that if someone knows more about *how* computers work, it becomes a lot easier to understand *what* they can do, and above all, what they cannot do.

In this book we will make a serious attempt to guide you through the principles that underlie computer systems. The term "computer systems" is to be taken in its broadest sense. It covers the field of relatively small personal computers, as well as that of worldwide networks consisting of millions of computers connected together to allow information to be easily communicated around the world.

# 1.1.2 Architecture versus organization

The approach that we have adopted is that of focusing on the **organization** of computers and networks. What does that mean? To make an easy comparison, suppose we had decided to write a book on the principles underlying cars. We could then roughly follow two approaches.

In the first approach, we could start by explaining that a car has an engine, and also explain what an engine consists of. We would be saying something about fan belts, cylinders, spark plugs, etc. And likewise, other necessary components that make up a car would be presented, together with an explanation of what they stand for. Putting it differently, we would follow an approach in which a car is successively decomposed into a number of **functional** components. In the end, you would be able to name all the necessary components and explain exactly what they stand for, and why they are needed. In that case, you would have a pretty good idea about the **architecture** of a car.

An alternative approach is the following. Rather than merely explaining that an engine is needed, we could choose to explain how that engine actually works. In that case, we would explain that an engine may have four cylinders, possibly arranged in a row, and that each cylinder is connected to a crankshaft. By pushing cylinders alternately downwards using compressed gas, we would show how an engine rotates the crankshaft that can then be subsequently used to rotate the wheels. Rather than just looking at *what* kind of components a car is made of, we would explain the principal working of each component, and the way that they are connected to each other. We would then be focusing on the **organization** of a car.

Admittedly, the distinction between architecture and organization is not a clear cut one. What should be clear, however, is that we are not going to focus on merely describing computer systems. Instead, our attention is focused on showing how the various components work, and how they are connected to each other. The main drawback of this approach is that we cannot tell what every computer looks like on the inside, and indeed, very many different organizations exist. In terms of our example above, we explain how a 4-cylinder engine works, and leave that of a 16-cylinder version to your own imagination.

At this point, let's start by gently introducing the various concepts that we will come

meet in succeeding chapters. In the next two sections we first concentrate on the concept of computers, followed by an introduction to computer networks.

# 1.2 Computers

The first part of this book, which consists roughly of Chapters 2 through 6, deals with explaining what computers actually are. An outline of our approach is explained in Section 1.2.1. Then, a structured approach to organizing computers is given in Section 1.2.2.

# **1.2.1** The essence of computing devices

The nomenclature applied to computers is illustrative of the way that they are conceived today. For example, it is not uncommon to blame the computer for not doing its job right, nor do we find it strange when someone says that the computer had a hard time getting calculations done. In the case of factory automation, as another example, computers are said to take over jobs that people previously did by hand. To take it one step further, computers are even said to be capable of *learning*. Many more examples can be thought of in which computers are not merely treated as appliances, but are perceived as autonomous entities having some kind of intelligence. The gap between our perception of what computers appear to be and what they really are is sometimes astonishing. Although it does make sense, for the sake of simplicity, to talk about computers as autonomous entities, it does not make sense to treat them as intelligent beings with a will of their own. Computers are not intelligent, and they cannot do anything that has not been put into them. They are just sometimes complex, that's all. In particular, they can be so complex that it is hard for one person to comprehend fully what computers really do. In this book we are going to explain some of the essentials of computers that will allow a person to get a grasp of how they work. We are convinced that this will help you put computers in the right perspective, namely that of useful appliances.

#### On simulation and interpretation

Let's start with saying something that might be surprising: computers have no concept of 0's and 1's. When giving the matter some thought, it is indeed hard to imagine that an electronic device can have any concepts. The essence of the matter is that computers are devices that *simulate* the way that we handle things. And they are doing such a good job at that, it is indeed sometimes hard to differentiate between simulation and what is really happening. Let's look at an example to illustrate this.

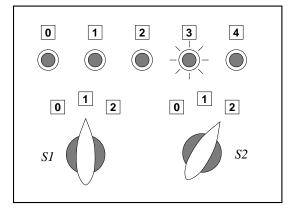

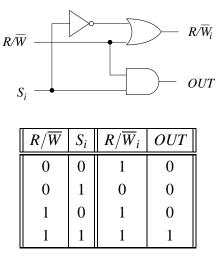

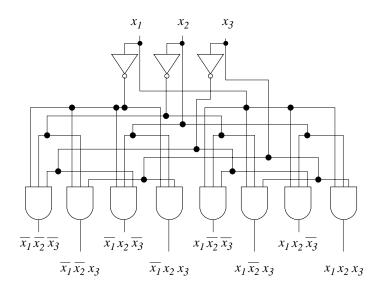

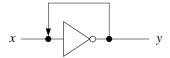

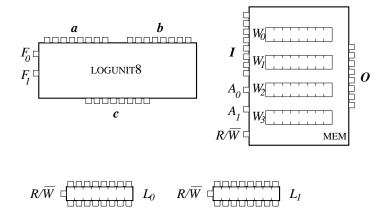

Suppose we had a box with five light bulbs and two switches as shown in Figure 1.1. The box hides an implementation of a simple calculator, capable of adding any combination of 0, 1, and 2. For example, if we set the first switch S1 to "0" and the second switch S2 to "2", then the third bulb marked "2" would light up. This would also be the case when S1 is set to "1" and S2 to "1" or, when S1 is set to "2" is set to "0".

Figure 1.1 A simple calculating device.

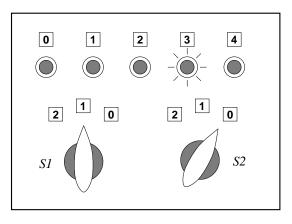

Figure 1.2 The effect of changing the labels: rubbish.

Now, the question that we want to raise here is whether or not our device can actually calculate.

Giving a straight answer to this question is really not easy. For one thing, it *appears* as if our device does have some calculation capabilities: no matter what combination of *S*1 and *S*2 we choose, it always gives the right answer. So, from that perspective, we would indeed say that we have a true calculator at our disposal.

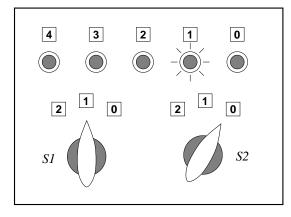

But suppose we changed the labels at both switches. Labels "0" are replaced by "2", and labels "2" are replaced by "0" respectively, as shown in Figure 1.2. In that case, the fact that a bulb starts to light really does not make any sense. Putting it differently, there is no sensible **interpretation** of what comes out of the box when we turn the switches. For one thing, our device is difficult to recognize as some kind of calculator. The crux of the matter lies, of course, in the way that we interpret the setting of the switches in combination with which bulb starts to glow. As a last experiment, you will see that everything works properly again if we also replace the label at each bulb as shown in Figure 1.3.

So what does our device actually do? First, it is important to realize that our calculator can only be perceived as such if we can interpret the setting of the switches in combina-

Figure 1.3 A working calculator again.

Figure 1.4 An implementation of our simple calculator.

tion with the light bulbs in a manner that makes sense to us. But there is more. It should be clear that the device itself has no "knowledge" built-in concerning arithmetic operations. Instead, what it does is merely **simulate** operations that have meaning to us. The combination of having the device properly simulate a part of our own world, and our own interpretation of its outcomes, puts us in a position to state that we indeed have a calculator at hand.

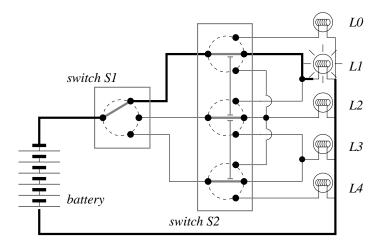

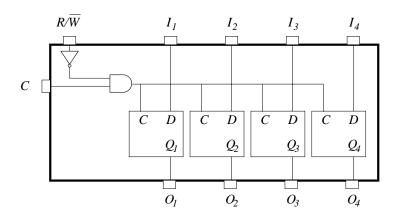

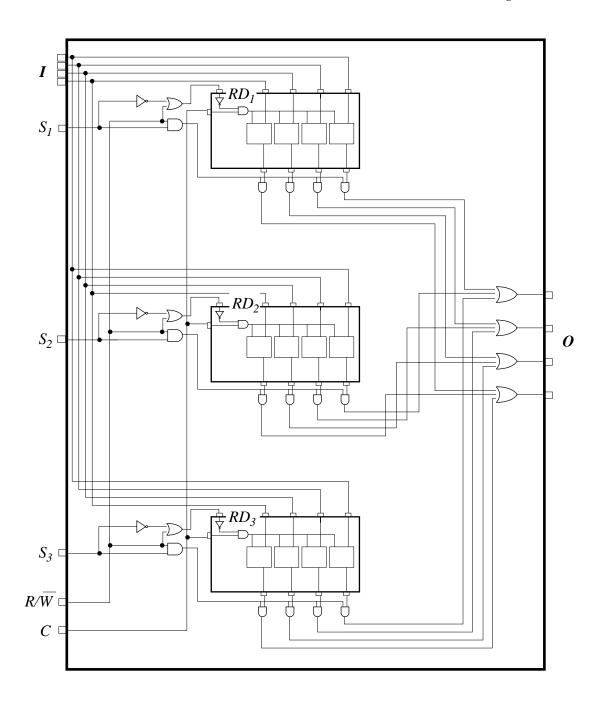

▷ Some of you might ask what our calculator looks like on the inside. An **implementation** is shown in Figure 1.4. Switch S1 is rather simple. It is just a switch that allows a person to choose to connect the input with precisely one of the three outputs. In the figure, the input is connected to the first output, in our case, meaning that switch S1 has been set to "0".

Switch S2 consists of three sub-switches, each sub-switch enabling the input to be connected to one of the three outputs. However, we assume that these three sub-switches are mechanically constructed in such a way that turning the knob always implies turning the three switches at the same time. Consequently, if the first sub-switch connects its input to

Figure 1.5 The principle of a programmable device.

its second output pin as shown in the figure, the other two sub-switches will do precisely the same in their case. What we have shown, therefore, is the state of affairs when switch S2 has been set to "1". And indeed, the light bulb marked L1 will now be fully connected to the battery, through which it then lights up.

Computers are in essence not very different from our simple calculator. They are constructed of electrical components that act as switches, such that if we feed them with the right electrical values (i.e. values to which we attach some useful interpretation) they will produce a set of output values in such a way that if we also interpret those values in some sensible manner it will appear as if our computer has really computed something worth while. The big difference with our calculator lies in the fact that real computers can be **programmed**.

#### **Programmable devices**

What do we mean exactly by a program? Following *Webster's Dictionary*, a **program** is "a plan or sequence of things to be done". For programmable devices, this can be reformulated as

A program is a sequence of instructions that are to be executed.

The keywords here are *instructions* and *execution*. For example, using our simple calculator for adding 1 and 2 could be done by executing the following two instructions:

set switch S1 to "1" set switch S2 to "2"

In this case, the user of the calculator would be responsible for the execution of these instructions; in computers, the execution mechanism is part of them. In that case, we need only construct a program and feed it into the device.

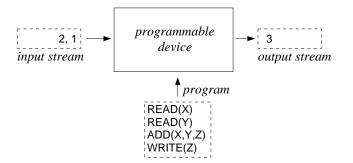

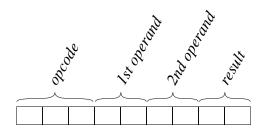

The principle is shown in Figure 1.5. What we see there is an *input stream* of numbers, and a *program* consisting of a series of instructions that the computer is to perform. The *output stream* consists of the results produced by executing the instructions on the given input. In our highly simplified example, we basically distinguish three types of instructions:

- The instruction READ(X) by which the *next* input value is read from the input stream and *internally stored* as the variable X.

- The instruction WRITE(X) of which the execution yields that the value of the internally stored variable X is written to the output stream.

- A collection of simple arithmetic operations that generally require three internally stored variables. For example, the instruction ADD(X,Y,Z) assigns the value of the operation X + Y to Z.

Using these three types of instructions, we can then, for example, construct the following general *program* that does the same as our calculator for an arbitrary input stream consisting of just two numbers:

```

READ(X)

READ(Y)

ADD(X,Y,Z)

WRITE(Z)

```

Programs are referred to as **software** to distinguish them from the hardware components of which computers are made.

Already we can see an important difference from our simple calculator. Where we first merely needed to turn the knobs of the two switches *S*1 and *S*2 in order to get the result instantaneously, we now have the situation that the input values are first *stored* internally in the form of the variables X and Y, respectively. Also, instead of immediately getting a result, we explicitly instruct the computer to do an addition, and again separately store this result as the variable Z. The result is made available to us by writing it to the output stream. We have thus assumed two extra components: an internal store, and some processing unit that operates on values kept in that store.

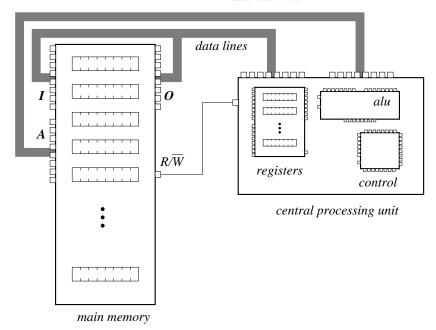

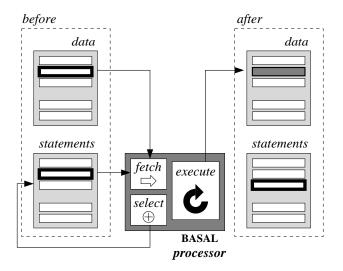

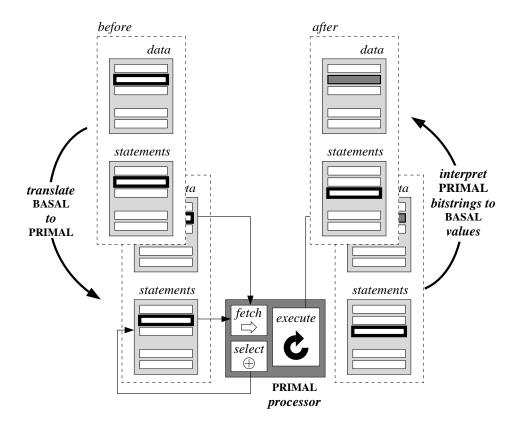

Figure 1.5 is a very simple way of representing computers, and is in fact the way that the first computers worked. The point to realize, however, is that in this architecture, each instruction is separately fed into the computer and subsequently executed. In particular, it requires a separate mechanism to read the program instruction by instruction in order to have it executed. An important improvement was made when it was recognized that programs need essentially not be treated differently from the input data that they worked on. The idea is revolutionary and simple at the same time. What we do is treat the instructions that make up a program as ordinary values that can be stored internally. In that case, our computer design can be made a lot simpler. What it means is that we need a powerful, **central processing unit** that is connected to a large **main store**. This central processing unit, or processor as it is called, essentially has just two operations built into it:

- An operation FETCH that reads the next instruction from the main store and stores it locally in a special variable INSTRUCTION.

- An operation EXECUTE that does precisely what its name suggests. It executes the instruction currently stored as the variable INSTRUCTION, and in turn internally stores the result in a special variable RESULT.

(We shall see in Chapter 3 that the variable RESULT is actually not needed. It is introduced here for the sake of illustration.) As we have said, the processor itself is a computer in its own right. It has some storage capacity and is capable of performing just two operations. That designing computers now becomes a lot simpler is not difficult to see. Essentially, we need to implement a device that *continuously* executes the alternating sequence of only the two operations FETCH and EXECUTE. Expressing this as a program yields something like:

```

forever loop

FETCH

EXECUTE

end loop

```

There are two important things that need to be kept in mind when organizing computers in this way. First, we need to make a distinction between two distinctive levels. At the lowest level we have the two operations FETCH and EXECUTE; one level higher we have instructions such as READ, WRITE, and ADD that are fetched from the main store and subsequently fed into the central processing unit, which in turn is responsible for their actual execution. In principle, you never see the two low-level operations: they have been directly implemented in the form of a processor.

Second, we will have to assume that the EXECUTE operation is capable of handling only a restricted number of instructions. In other words, we may not expect that every possible high-level instruction that we can think of can be executed by the EXECUTE operation. Putting it differently, we say that EXECUTE **implements** a fixed set of instructions, also known as the processor's **instruction set**. Programming a computer then consists of telling it what to do by constructing valid sequences of instructions taken from this instruction set.

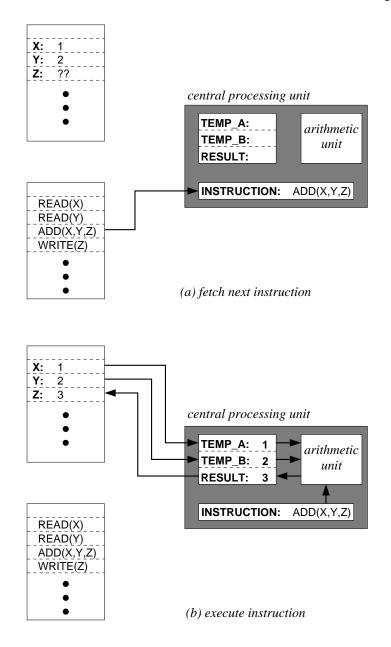

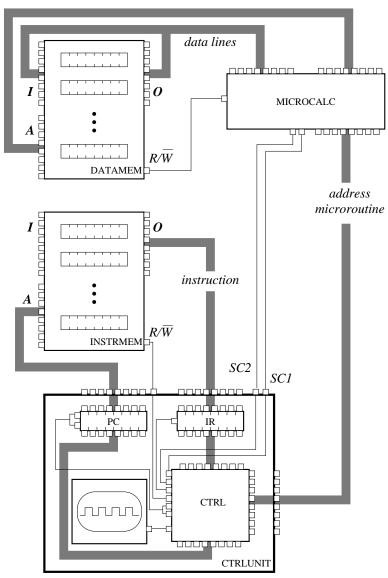

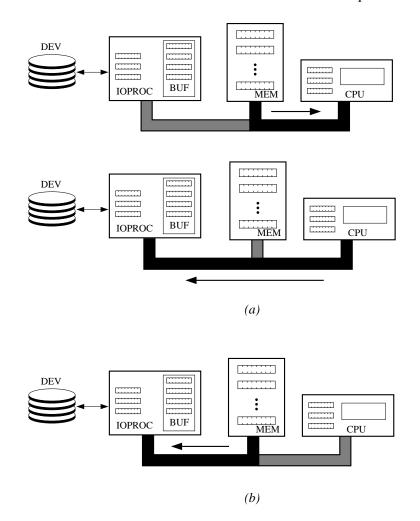

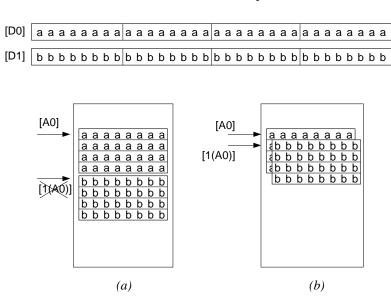

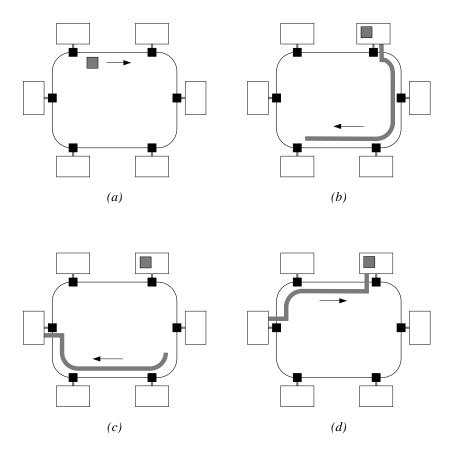

Using this approach, we can now show how computers are generally organized. In Figure 1.6 we have a distinction between two types of stores. One type is for storing values that come from the input stream as well as those for the output stream, and one type is for storing programs. We shall see later that these two stores can be taken together. Figure 1.6(a) shows what happens when the instruction ADD(X,Y,Z) is fetched; Figure 1.6(b) what happens when this instruction is executed by the processor.

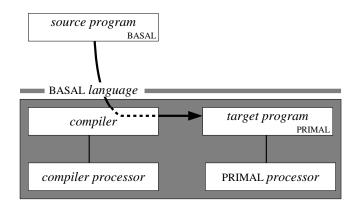

### **1.2.2** The concept of a multi-level machine

Making a distinction between the two levels as discussed above simplified computer design considerably. The important issue was that designers need now concentrate mostly on just the implementation of the two operations FETCH and EXECUTE. The result would be a processor that could subsequently execute any instruction that EXECUTE could handle. But as you may imagine, implementing EXECUTE in itself is not an easy task to accomplish. In particular, in order to keep the complexity of the processor manageable, the set of instructions that can be handled generally consists of instructions that are still rather primitive. And in that respect, nothing much has changed over the years.

Having to use only primitive instructions is awkward when constructing large pro-

**Figure 1.6** The organization of a computer in which an instruction is fetched (a) and subsequently executed (b).

grams. What effectively happens is that although the complexity of computer design can be greatly reduced if only primitive instructions are supported, the complexity of programs (that can only make use of these instructions) increases. This is comparable to some domestic appliances, most notably perhaps video recorders. What we see there is that the cheaper ones provide you with just simple buttons to operate the recorder. Programming the recorder can then indeed be a rather frustrating undertaking especially if a mistake is made somewhere. In that case, it will generally be necessary to start all over again. Modern recorders avoid this by sometimes providing just a single instruction that

you have to execute, namely scanning the bar code as it appears in TV guides. And although it does make things simpler, the additional price paid for this facility reflects that the underlying technology can indeed be relatively difficult to realize.

Programming computers is not much different in this respect. Constructing programs that are built from primitive instruction sets is generally a cumbersome and error prone process. Two complementary solutions have been sought to alleviate these problems: high-level programming languages and operating systems.

#### **High-level programming languages**

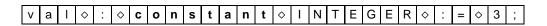

There are various high-level programming languages. In this book our primary focus is on the use of a "conventional" high-level language which will be presented in Chapter 4. Conventional high-level programming languages allow us to arrange programs as a collection of **statements**, embedded in relatively small program units, of which the **procedure** is probably the best known. Consider the following example.

Suppose we want to write a program by which we can multiply two (positive integer) numbers M and N, and store the result in a variable P. This would be a simple task as all popular high-level programming languages support a multiplication operation. For example, we can simply use the language's **assignment statement** such as

P := M \* N;

of which the execution will show that the result of the multiplication M \* N is assigned to the variable P.

Now, as it may seem that there is a multiplication operation available, this becomes less obvious if you know exactly how multiplication is to be performed. For example, some computer designers have deliberately omitted a multiplication instruction to keep their computers as simple as possible. This means that we have to write our own multiplication program if necessary. To illustrate how this could be achieved by means of a high-level language, let's also assume that there is no multiplication facility at *that* level as well. In that case, we can calculate M \* N through repeated addition, i.e.

$$\mathsf{P} := \underbrace{\mathsf{M} + \cdots + \mathsf{M}}_{\mathsf{N} \text{ times}}$$

which can easily be expressed in a high-level programming language as follows:

$\begin{array}{ll} (1) & R := 0; \\ (2) & P := 0; \\ (3) & \textbf{while } R < N \ \textbf{loop} \\ (4) & P := P + M; \\ (5) & R := R + 1; \\ (6) & \textbf{end loop} \end{array}$

In the first line, we are initializing an additional variable R that is going to act as a *counter*. It counts how many times we have already added M to P. The latter is initialized in the second line. Lines (3)–(6) are an example of a so-called **while** statement that is supported

#### Computers 11

Figure 1.7 Viewing a computer as consisting of three distinct levels of instructions.

by almost every high-level language. In our case, we have simply stated that as long as we have not added M a sufficient number of times to P, we have to do another addition. The latter is done through the assignment statement in (4), whereas in line (5) we increment our counter by one.

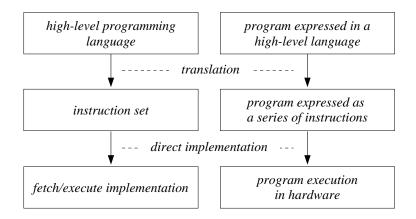

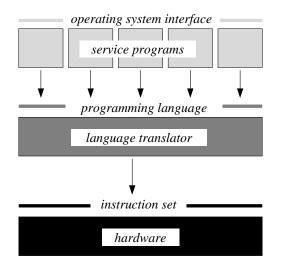

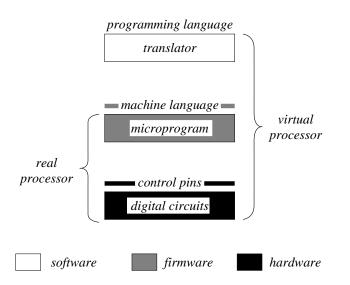

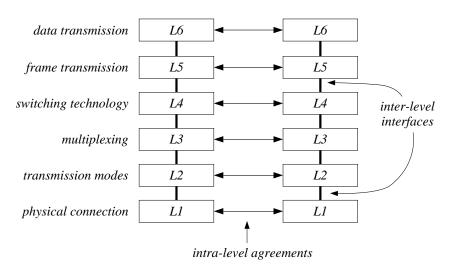

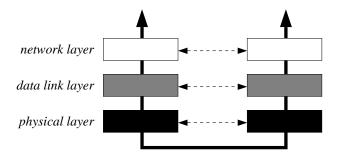

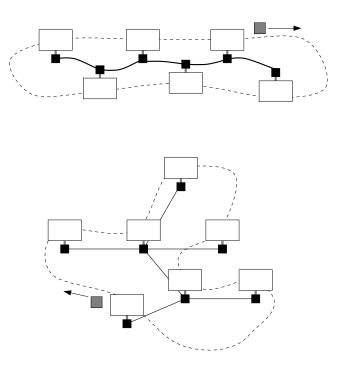

It is not difficult to see that our small program is correct, and indeed fairly easy to understand. We will have much more to say about programs such as the one above, and we shall also illustrate that using high-level programming languages is much simpler to do than using rather primitive instruction sets. There is, however, a problem. There is no processor that can execute any program written in a high-level language. The only thing that a processor can do is handle programs that use instructions from its instruction set. The solution to this problem is found in *language translation*. What we can do is translate programs written in a high-level programming language into equivalent programs, but now expressed as a series of instructions that a processor can handle. Taking into account that instruction sets are in turn implemented through a fetch/execute mechanism, we can then show a computer as a multi-level machine as shown in Figure 1.7.

There are some intricacies related to translating programs expressed in a high-level language to a lower-level instruction set, but we shall postpone further discussion on this subject until Chapter 4. The important point to note now is that we are gradually making a computing device more easy to use by allowing more powerful programming constructs, even if we do not immediately have an implementation of these constructs at hand. Instead, we provide a translation mechanism from one language to another where needed. The advantage is that from a user's perspective the only thing that matters is what the programming language looks like, as this is the only interface to a computer that allows one to set it to work. And taking it from that perspective, a high-level programming language makes a computer look like a powerful and easy device to use. We return to this issue below after having introduced yet another concept that eases the use of computers.

#### **Operating systems**

Using high-level languages is not the only way to ease the construction of computer programs. In particular, it is not hard to imagine that having just a bare computer requires that parts of any program will have to be devoted to handling all kinds of input and output operations for transferring data between a peripheral device and the computer. For example, when using a disk, you would need a way to retrieve data from that disk, and also be able to store data on it. This would involve *controlling* the device by setting its read/write heads, doing the actual data transfer, etc. The whole point is that these parts of a program in essence have little to do with the main purpose of using the computer. But no matter what program is being developed, we will probably have to control input and output of data in any case. In that sense, it would be a lot easier if we could make use of a **service program** that handles disk manipulations. Such a service program would have to be constructed only once and could be subsequently used as part of the various other programs that are constructed. And things would be even better if someone else had constructed such a service program for us, preferably an expert in the field of writing programs that allowed us easily to make use of the hardware facilities of a computer.

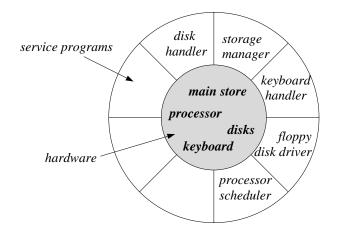

From a certain perspective, this is exactly what so-called **operating systems** are made of: a large collection of general-purpose service programs for controlling the computer and its peripheral devices. Operating systems roughly establish two things. First, they make the life of programmers a lot easier by means of their service programs. Effectively, a service program establishes that you need no longer be concerned about how some of the computer's facilities such as disks are actually to be used, as this is completely taken care of. In other words, a service program provides an *easy* way of programming a computer. Second, service programs can be highly optimized once and for all so that these facilities are also used *efficiently*. Operating systems can thus be viewed as *resource managers*.

An important side-effect of operating systems is that from a programming perspective, you never see how this control of resources takes place. Putting it differently, service programs shield all kinds of intricacies that are related to controlling the hardware. As a consequence, the computer appears to the programmer only by means of the service programs that are part of the operating system. The service programs form a layer over the hardware. This principle is illustrated in Figure 1.8.

But if service programs hide all kinds of hardware details, and by doing so ease program construction, have we not then constructed an abstract view of what a computer actually is? Indeed, this is the case and you might say that an operating system combined with the underlying hardware is a realization of a **virtual machine**: a device that appears to be something different from its hardware components. This is, in principle, not much different from using a high-level programming language as discussed above. A high-level programming language provides a view of a computer's programming capabilities which are more extensive than actually provided. Operating systems establish similar goals, but in a different way. In both cases, the computer appears to be a more powerful device than is reflected by the hardware.

A question that comes to mind, is how operating systems and high-level languages are

**Figure 1.8** An operating system viewed as a collection of service programs shielding the hardware.

Figure 1.9 The construction of a virtual, multi-layered computing machine.

related to each other. There are different ways of viewing this relationship, but the one we shall take in this book is the following. The essence of the matter lies in how we construct service programs. In this book we shall demonstrate that this can be done by means of a high-level programming language. Consequently, we will be constructing service programs that are aimed at controlling a computer's resources, but will use the programming facilities as provided by some high-level programming language. This leads to further enhancement of our concept of a multi-level machine, as is shown in Figure 1.9.

And this is about as far as we shall go. It is not hard to imagine, however, that we can easily continue our line of reasoning by constructing yet another layer on top of an operating system. Typically, such a layer will further extend our view of what a computer can actually do, but at the same time will probably narrow our view as well in the sense that the presented capabilities will be more focused towards a particular *application domain*.

To illustrate, consider a modern word processing system such as those that are used for personal computers. The main purpose of such a system is to provide its users with all kinds of facilities for making documents. The instructions that are entered either through commands (such as combinations of keystrokes) or by means of a mouse (if a more advanced graphical interface is supported) allow you to move the cursor, display a specific portion of a document on the screen, generate a table of contents, etc. At the same time, word processing systems do a lot more. For example, they allow us to manage the storage of documents into files and directories. Also, they provide all kinds of ways for handling printing devices, help organize the screen, or even allow us to completely redefine the meaning of the keys on a keyboard. The last facilities are traditionally provided by operating systems. And if making documents is the only thing that is done with a computer, there may be no reason why someone should ever use another program. Indeed, in such cases the computer appears to its user as nothing but an advanced word processing device, again yet another virtual multi-level machine.

# **1.3** Computer networks

However, explaining how word processing systems and the like are constructed is not what we are interested in here. Instead, rather than building layers of software on top of each other, we will primarily be concerned with extending layers in such a way that *communication* between computers and their users becomes possible. We will thus enter the realm of **computer networks** which forms the topic of the second part of this book. Let's first consider why computer networks are so convenient to have.

# **1.3.1** The demand for computer networks

Linking computers to each other is attractive for a number of reasons, of which three important ones immediately come to mind:

• **Resource sharing.** This is a phenomenon with which most of us who have ever worked with computers connected in a network are already familiar. The most notable shared resources are perhaps printers. To date, good high-quality printers are still costly, especially if the combination of speed and quality is a major concern. But although a printer is typically something that is generally needed, it is not something that is needed all the time. This makes them ideal for sharing among several users, which in turn requires that those users can all have easy access. Hooking a printer into a network is a solution to that problem. But there are many other shared resources as well, although not always as visible to users as printers. An important type of shared resource is software. For example, it is a lot cheaper for an organization to buy just a single copy of some advanced word processing system, and keep that copy at one location. If someone wants to do word processing, they must collect the software from that single location and have it executed on his or her own computer. Getting the word processing system onto a computer is a lot easier if this can be done via a network.

- Shared information. This is an extremely important reason for linking computers together. Sharing information by having a database system as part of a computer network allows remote users located at different sites, all to have access to the same data. Typical examples of computer networks set up for sharing information are (electronic) banking systems, airline reservation systems, stock inventory systems used in e.g. supermarkets, and online library catalogs. Many more will come to mind. Sharing information through a computer network is practical for a number of reasons. First, it is a relatively easy way to allow users located at completely different sites to have easy access to a single source of information. Another important reason is that this construction allows the information to remain consistent (although this is not always an easy task to accomplish). If one user performs an update, then this change will be visible to all other users as well.

- **Information exchange.** This is going to be a main focus for us when discussing computer networks communication between users and programmers. We shall see that computer networks offer important opportunities for users to exchange information, often much better than is currently possible via hand-delivered mail, telephones, faxes, etc. Computerized forms of standard communication facilities are becoming increasingly popular. For example, electronic mailing facilities have shown to be extremely useful: not only is it easy to get in touch with someone, it is also very efficient (it often just takes a few seconds, or at worst, a few minutes to get electronic mail to the other side of the world). As another example, exchanging documents over a computer network allows users to collaborate without having to be located at the same site. In the same way, it can be anticipated that participating in a so-called *video conference* with participants from all over a country or even the world will enhance ease of communication.

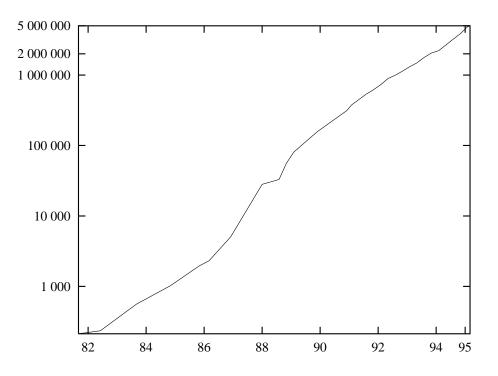

Just as we have become used to computers, we now also find it natural that computers are linked together into a network. The most dominant growth of computer networks has no doubt taken place in offices, factories, and of course, in universities and research institutes. Especially in the last two cases great efforts are seen in expanding networks to cover larger areas, and to improve the quality of the connections. These efforts are now gradually finding their spin-offs in the construction of networks that are commercially attractive to larger groups. For example, many banks today offer various services that allow people to perform parts of their financial administration through a personal computer. The French Minitel project that connects millions of homes to centralized information servers is another example of bringing computer network technology into our homes. The exponential growth of the worldwide Internet (which is discussed in Chapter 9) is sometimes beyond imagination, and as of today, services available on the Internet are readily available to many. Finally, as a last example, we may expect that in the near future the telephone companies will provide us with integrated services for communicating voice, data, and pictures through ISDN or related full digital networks.

### **1.3.2** Some fundamental problems

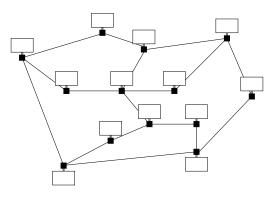

Having grasped the essentials of what a computer is all about, it becomes a lot easier to conceive how we can subsequently link computers together. Again, starting from first principles helps in understanding what the problems and their solutions are, and this is the approach that we have adopted in the second part of this book. In particular, as we gradually expose the workings of computers, we shall also present computer networks by discussing problems as they surface with the growth of a network in terms of its number of computers and geographical coverage.

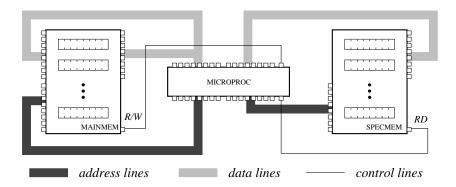

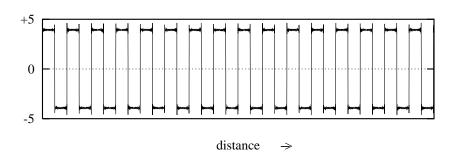

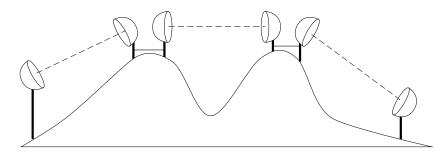

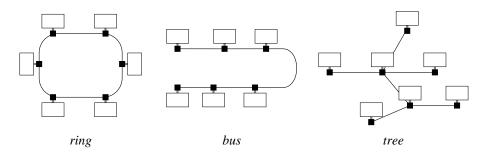

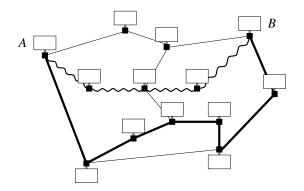

The first type of computer network that we shall consider is a simple one. It consists of two computers that are linked together through some kind of **transmission medium**. There are various transmission media. Roughly, a distinction is made between guided and unguided media. Guided media are, for example, wires through which an electrical or optical signal is sent that represents the data we want to transmit. Unguided media are, for example, radio transmission and satellite connections. In that case, data is sent in the form of radio signals.

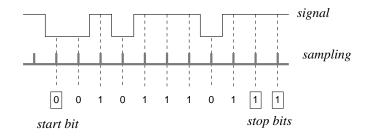

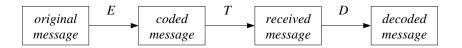

In order to transmit data from one computer to another, we encode it as some kind of signal that is subsequently sent across the transmission medium. In general, such a signal represents a so-called **bit string**, which in turn represents the data we want to transmit. A bit string is a series of *ones* and *zeroes*. Again, we emphasize that it is not the bit string that is being sent, but rather a signal representing that bit string. Nevertheless, when talking about data communication, it is a lot easier to think of it in terms of bit strings rather than signals, and we shall adopt this convention here.

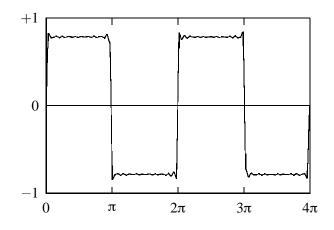

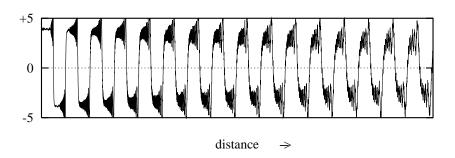

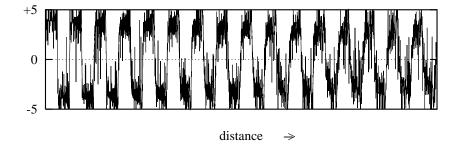

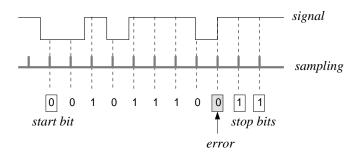

#### **Transmission errors**

Now, sending bit strings from one computer to another seems a straightforward thing to do. However, this statement is not entirely true. The first problem that we are confronted with when we link two computers together is that our transmission medium will have some bounded quality with respect to its transmission capabilities. In particular, in many cases there is a low but non-negligible probability that transmission errors may occur. The effect of a transmission error is that a bit string **b** which is sent at one end of the transmission medium may arrive as a *different* bit string **b** at the other end. This problem is caused by many factors, but above all, it becomes more apparent as the length of the transmission medium increases. For this reason alone, transmission errors occur less frequently in a single computer as the connections between the various components in that case are relatively short.

One way or the other, we have to account for the fact that a bit string that arrives at a receiver may contain errors in the sense that it is different from the bit string that was originally sent. Devising schemes by which we can *detect* that a received bit string can never correspond to what was originally sent is an important subject when developing computer networks. There are all kinds of ways that errors can be detected, and some of the important ones will be discussed in Chapter 7. To give you a flavor of how error detection schemes work, consider the following.

limited bandwidth  $\Rightarrow$  traffic jam

Figure 1.10 The phenomenon of limited bandwidth illustrated by road traffic.

To simplify matters, suppose we wish to transmit the series of decimal numbers  $\mathbf{d} = \langle 2, 3, 4, 5 \rangle$ . In that case, we can choose to extend this series with an additional number by summing its values, leading to the series  $\mathbf{e} = \langle 2, 3, 4, 5, 14 \rangle$ . It is this series  $\mathbf{e}$  that we then transmit. Now, suppose that the receiver eventually picks up the series  $\hat{\mathbf{e}} = \langle 2, 4, 4, 5, 14 \rangle$ . In that case it can conclude that something went wrong for the simple reason that  $2+4+4+5 \neq 14$ , which it would have expected in the first place. That this scheme does not always work is easily seen when considering that the receiver cannot detect that the series  $\langle 1, 4, 4, 5, 14 \rangle$  also contains errors.

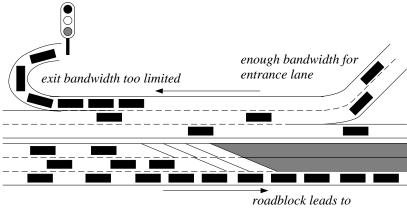

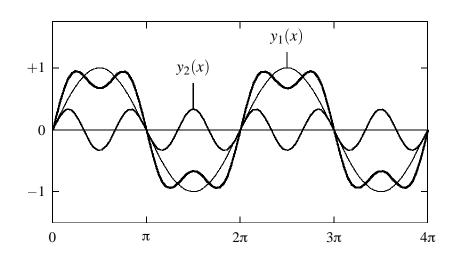

#### Limited bandwidth

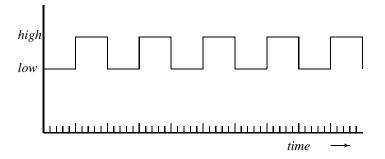

Perhaps more serious when communicating between two computers is the fact that there is an upper bound to the amount of data that can be sent per time unit. This is generally expressed by the number of transmitted **bits per second** (bps). The two limiting factors here are the type of transmission medium and the computers themselves. There is an easy comparison to this phenomenon by considering road traffic. A highway is comparable to the transmission medium. The amount of traffic that can pass per hour depends on the number of lanes that are available. Likewise, the entrance and exit lanes determine how many cars can actually get on and off the highway, and as such are comparable to the transmission capabilities of the sending and receiving computer, respectively. This is illustrated in Figure 1.10.

What we see here are three potential bottlenecks that may cause **congestion**. First, an entrance lane may not be capable of handling all the traffic, despite the fact that the road itself at that point has enough capacity. In our example, we have shown an entrance lane that will presumably not lead to these kind of congestion problems. A second potential bottleneck is shown at the point where the three lanes are merged into one. In that case, it is the road that causes a traffic jam. Finally, our example also shows that an exit may also lead to traffic jams if not properly designed.

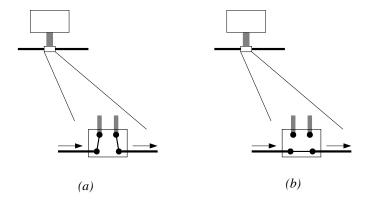

Figure 1.11 The effect of not properly balancing the work on a conveyor belt.

At present, computers as well as the transmission media that connect them may impose serious problems with respect to communication. With the introduction of new transmission technology, such as optical fiber, the problem is gradually shifting towards computers. What it means is that we have to find a way such that (1) computers can work at a pace that meets our needs for transmitting large amounts of data, and (2) that computers can adjust to each other's pace with respect to communication. We will return to the first issue on several occasions in later chapters. The second issue is the problem of **flow control** which we illustrate next.

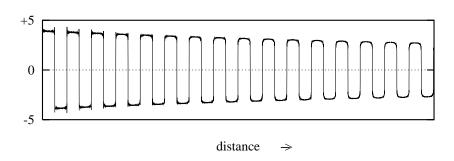

#### The producer-consumer problem

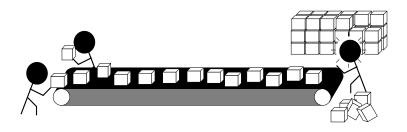

Assume that two computers are connected through an ideal transmission medium (that such a medium does not exist is something we are not concerned about here). In that case, there is at least one issue that we will have to deal with, namely the difference in transmission speeds between the sender and the receiver, respectively. What do we mean by this? The problem is easily illustrated by comparing what happens if we put two workers on one end of a conveyor belt and only one person on the other end, as illustrated in Figure 1.11. For the sake of argument, assume that each box contains priceless chinaware.

The problem is that the two workers that put boxes onto the belt jointly operate at such a speed that it is almost impossible for the person on the other end to catch all the boxes and stack them. Consequently, a large number of the boxes will simply drop off the belt and their contents will be lost.

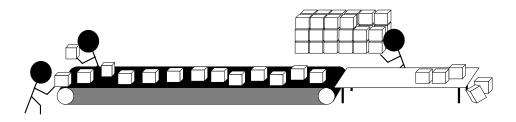

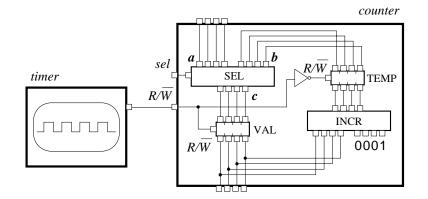

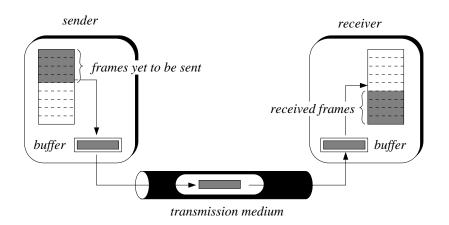

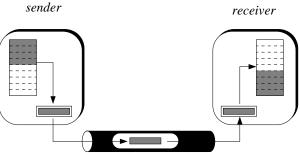

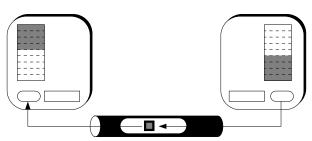

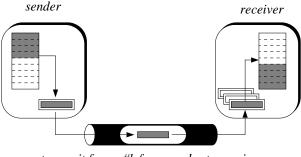

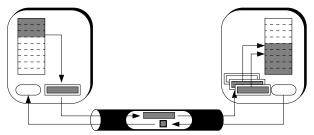

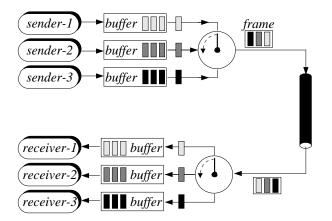

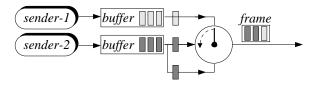

The same problem happens with computers. If a receiver is not capable of processing incoming data at the same speed at which a sender is transmitting it, data will simply be lost. To a certain extent, the problem can be solved through the use of **buffers**, as shown in Figure 1.12. What is seen there is that if a box is not immediately removed from the belt it will be stored automatically in a special area. But as soon as that area is full, boxes will start dropping off the belt again.

The whole idea of using buffers is to smooth the discrepancies in transmission speed between a sender and a receiver. If the sender stops sending for a while, the receiver can at least make up time by processing the data that has been stored temporarily in its buffers. Obviously, this scheme will only work if the sender does eventually stop transmission before the receiver's buffers are all full, or at least temporarily reduces the speed at which

Figure 1.12 Using a buffering area to assist removal of boxes.

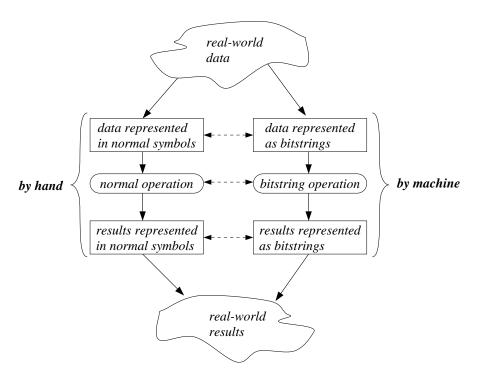

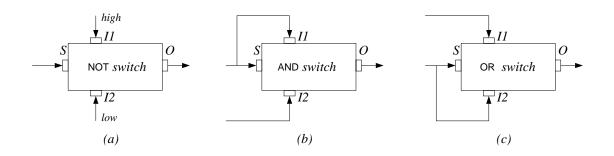

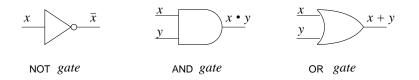

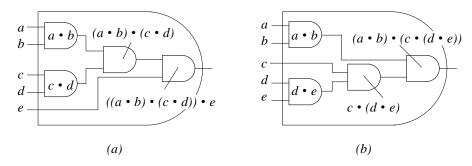

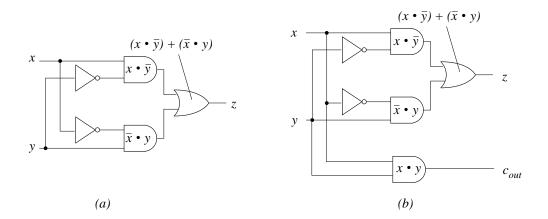

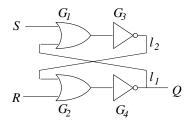

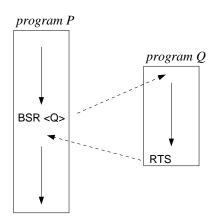

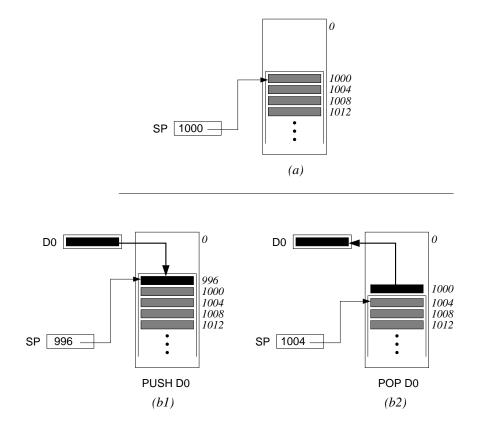

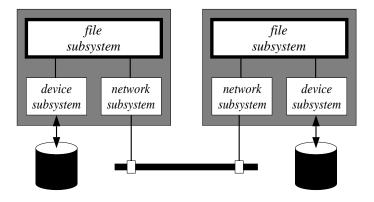

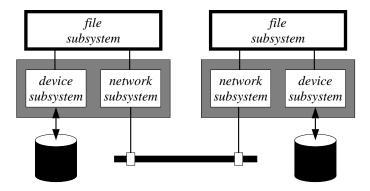

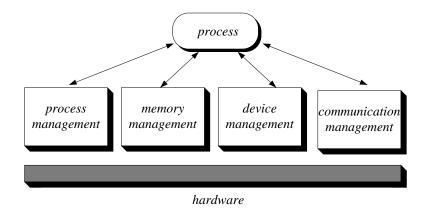

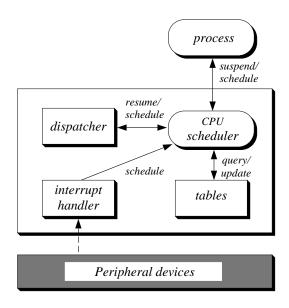

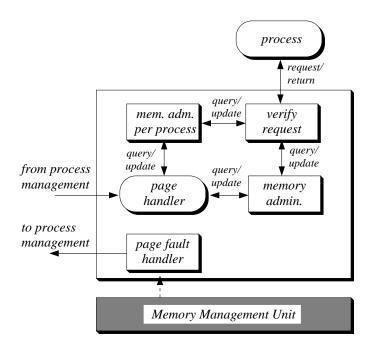

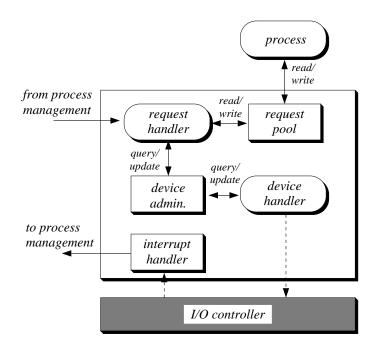

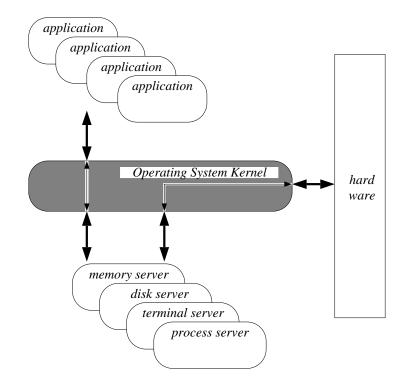

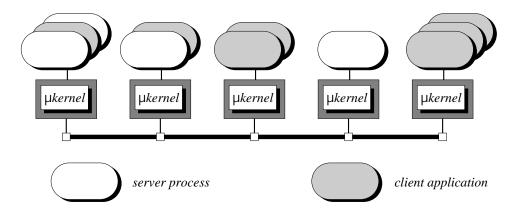

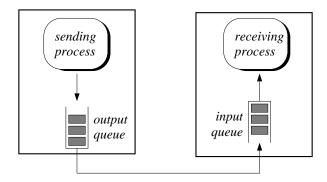

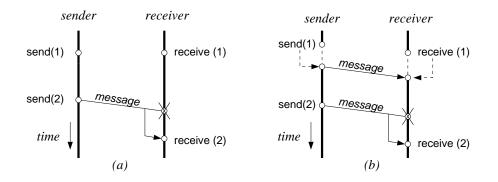

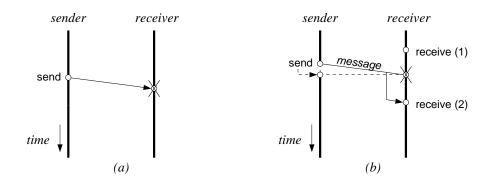

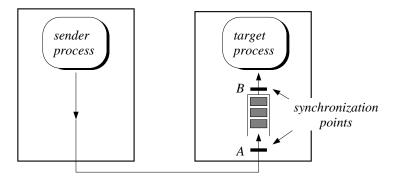

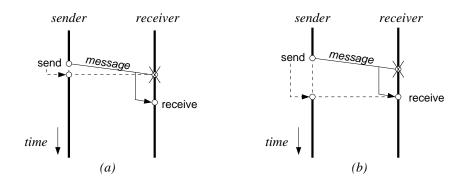

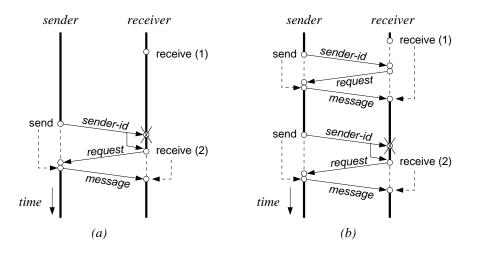

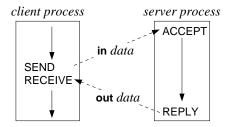

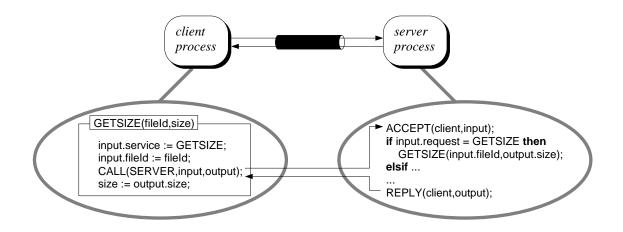

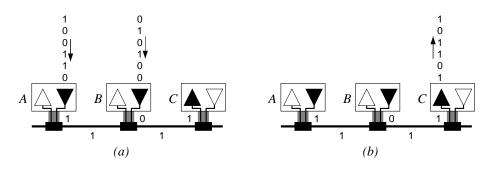

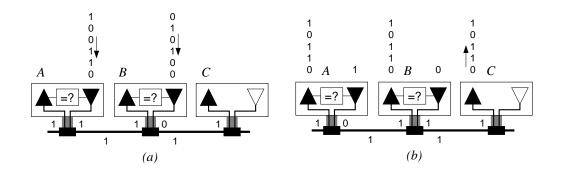

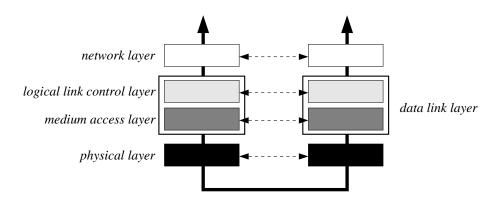

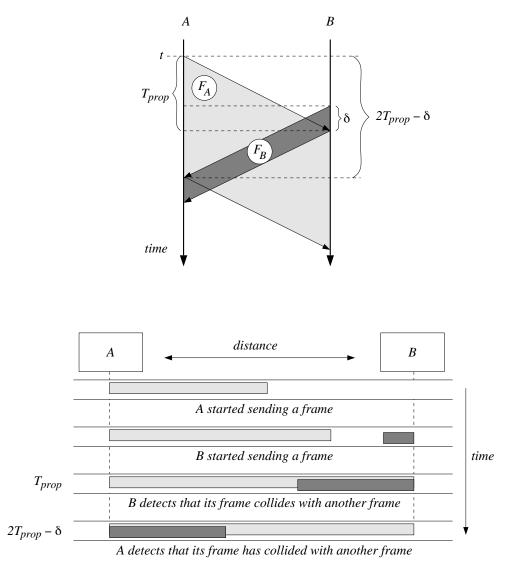

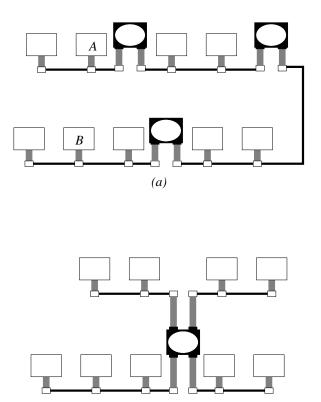

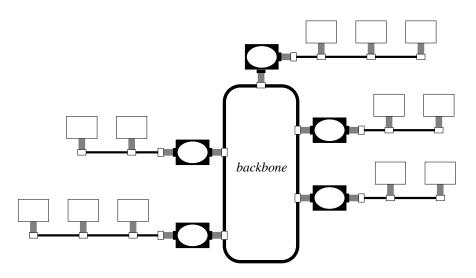

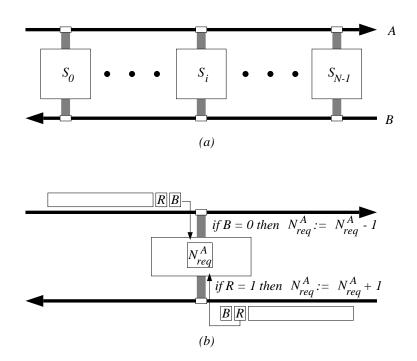

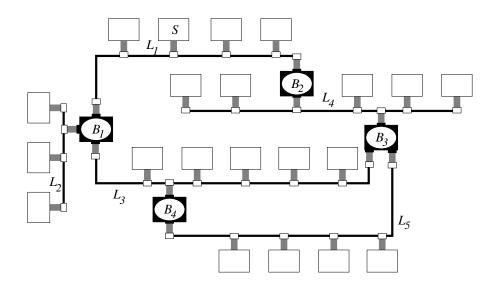

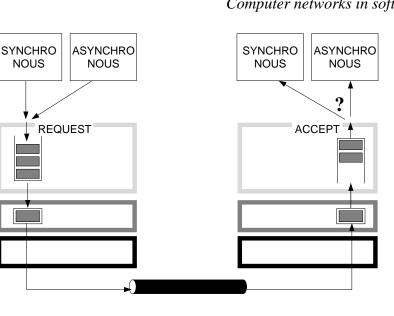

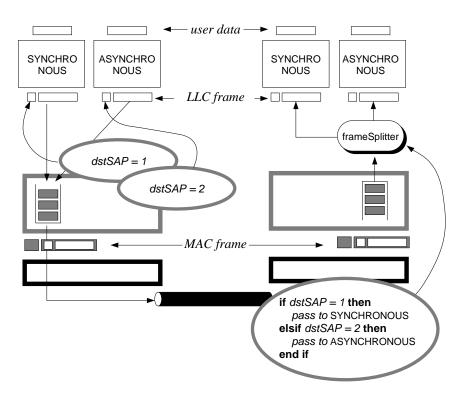

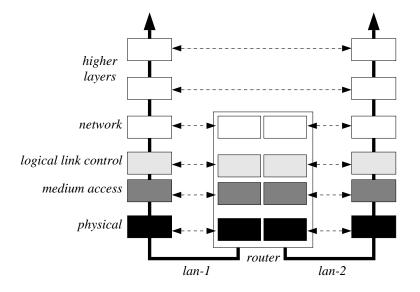

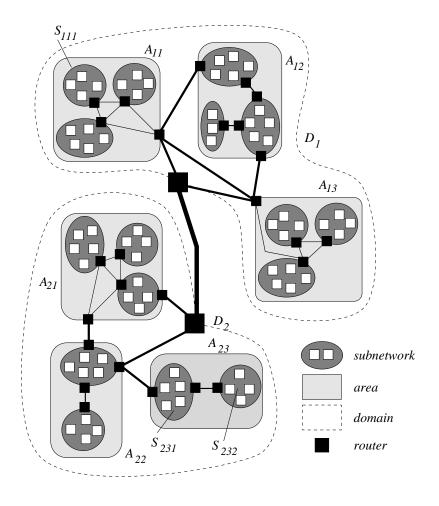

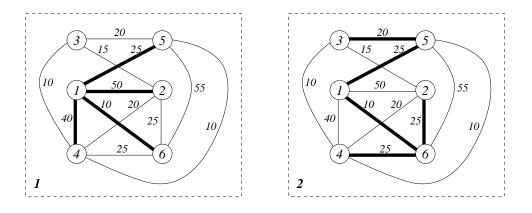

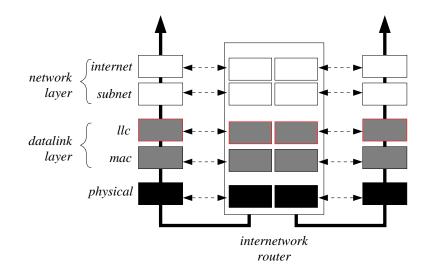

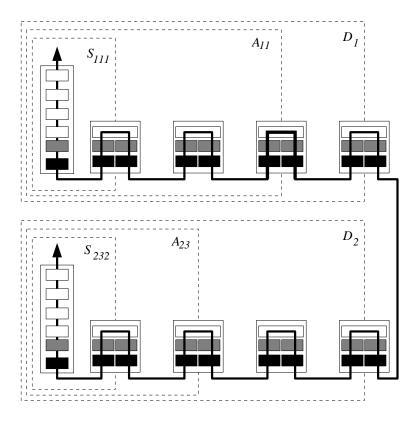

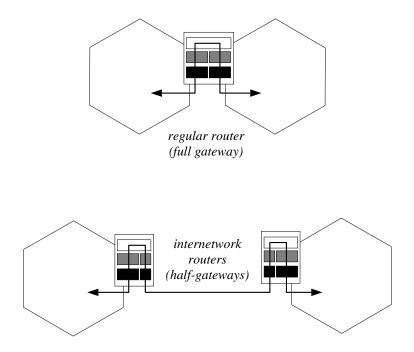

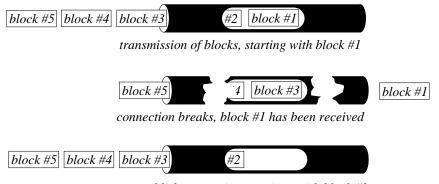

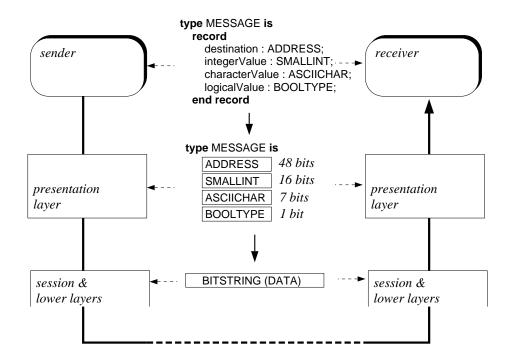

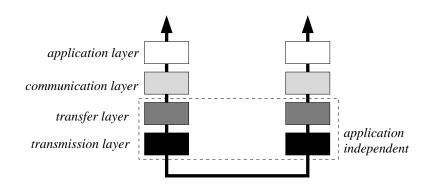

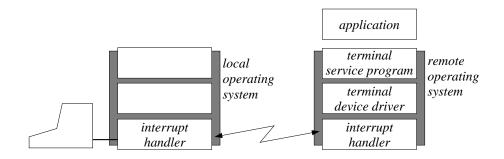

it transmits data. But as soon as buffers are full, we fall back into the situation described above: incoming data simply has to be discarded by the receiver.