Overview

```

* 6.828 goals

* Understand operating system design and implementation

* Hands-on experience by building small O/S

* What is the purpose of an O/S?

* Support applications

* Abstract the hardware for convenience and portability

* Multiplex the hardware among multiple applications

* Isolate applications in order to contain bugs

* Allow sharing among applications

* Provide high performance

* What is the O/S design approach?

* the small view: a h/w management library

* the big view: physical machine \rightarrow abstract one w/ better properties

* Organization: layered picture

h/w: CPU, mem, disk, &c

kernel services

user applications: vi, gcc, &c

* we care a lot about the interfaces and internal kernel structure

* What services does an O/S kernel typically provide?

* processes

* memory allocation

* file contents

* directories and file names

* security

* many others: users, IPC, network, time, terminals

* What does an O/S abstraction look like?

* Applications see them only via system calls

* Examples, from UNIX (e.g. Linux, OSX, FreeBSD):

fd = open("out", 1);

write (fd, "hello\n", 6);

pid = fork();

* Why is O/S design/implementation hard/interesting?

* the environment is unforgiving: quirky h/w, weak debugger

* it must be efficient (thus low-level?)

...but abstract/portable (thus high-level?)

* powerful (thus many features?)

...but simple (thus a few composable building blocks?)

* features interact: `fd = open(); ...; fork()

* behaviors interact: CPU priority vs memory allocator

* open problems: security; performance

* You'll be glad you learned about operating systems if you...

* want to work on the above problems

* care about what's going on under the hood

* have to build high-performance systems

* need to diagnose bugs or security problems

Class structure

* See web site: https://pdos.csail.mit.edu/6.828

* Lectures

* 0/S ideas

* detailed inspection of xv6, a traditional O/S

* xv6 programming homework to motivate lectures

* papers on some recent topics

```

\* Labs: JOS, a small O/S for x86 in an exokernel style

```

* you build it, 5 labs + final lab of your choice

* kernel interface: expose hardware, but protect -- few abstractions!

* unprivileged user-level library: fork, exec, pipe, ...

* applications: file system, shell, ...

* development environment: gcc, qemu

* lab 1 is out

* Two exams: midterm during class meeting, final in finals week

Introduction to system calls

* 6.828 is largely about design and implementation of system call

interface. let's look at how programs use that interface.

we'll focus on UNIX (Linux, Mac, POSIX, &c).

* a simple example: what system calls does "ls" call?

* Trace system calls:

* On OSX: sudo dtruss /bin/ls

* On Linux: strace /bin/ls

* so many system calls!

* example: copy input to output

cat copy.c

cc -o copy copy.c

./copy

read a line, then write a line

note: written in C, the traditional O/S language

* first read/write argument is a "file descriptor" (fd)

passed to kernel to tell it what "open file" to read/write

must previously have been opened, connects to file/device/socket/&c

UNIX convention: fd 0 is "standard input", 1 is "standard output"

* sudo dtruss ./copy

read (0x0, "123 \n \0", 0x80)

= 4 0

write(0x1, "123 n@ 213 002 0", 0x4)

= 4 0

* example: creating a file

cat open.c

cc -o open open.c

./open

cat output.txt

note: creat() turned into open()

note: can see actual FD with dtruss

note: this code ignores errors — don't be this sloppy!

* example: redirecting standard output

cat redirect.c

cc -o redirect redirect.c

./redirect

cat output.txt

man dup2

sudo dtruss ./redirect

note: writes output.txt via fd 1

note: stderr (standard error) is fd 2 -- that's why creat() yields FD 3

* a more interesting program: the Unix shell.

* it's the Unix command-line user interface

* it's a good illustration of the UNIX system call API

* some example commands:

1s

1s > junk

1s | wc -1

1s | wc -1 > junk

* the shell is also a programming/scripting language

cat > script

echo one

echo two

sh < script

```

```

* the shell uses system calls to set up redirection, pipes, waiting

programs like wc are ignorant of input/output setup

* Let's look at source for a simple shell, sh.c

* main()

basic organization: parse into tree, then run

main process: getcmd, fork, wait

child process: parsecmd, runcmd

why the fork()?

we need a new process for the command

what does fork() do?

copies user memory

copies kernel state e.g. file descriptors

so "child" is almost identical to "parent"

child has different "process ID"

both processes now run, in parallel

fork returns twice, once in parent, once in child

fork returns child PID to parent

fork returns 0 to child

so sh calls runcmd() in the child process

why the wait()?

what if child exits before parent calls wait()?

* runcmd()

executes parse tree generated by parsecmd()

distinct cmd types for simple command, redirection, pipe

* runcmd() for simple command with arguments

execvp(cmd, args)

man execvp

ls command &c exist as executable files, e.g. /bin/ls

execvp loads executable file over memory of current process

jumps to start of executable -- main()

note: execvp doesn't return if all goes well

note: execvp() only returns if it can't find the executable file

note: it's the shell child that's replaced with execvp()

note: the main shell process is still wait()ing for the child

* how does runcmd() handle I/O redirection?

e.g. echo hello > junk

parsecmd() produces tree with two nodes

cmd->type='>', cmd->file="junk", cmd->cmd->cmd-...

cmd->type=' ', cmd->argv=["echo", "hello"]

the open(); dup2() causes FD 1 to be replaced with FD to output file

it's the shell child process that changes its FD 1

execvp preserves the FD setup

so echo runs with FD 1 connected to file junk

again, very nice that echo is oblivious, just writes FD 1

* why are fork and exec separate?

perhaps wasteful that fork copies shell memory, only

to have it thrown away by exec

the point: the child gets a chance to change FD setup

before calling exec

and the parent's FD set is not disturbed

you'll implement tricks to avoid fork() copy cost in the labs

* how does the shell implement pipelines?

$ 1s | wc -1

* the kernel provides a pipe abstraction

int fds[2]

pipe (fds)

a pair of file descriptors: a write FD, and a read FD

data written to the write FD appears on the read FD

* example: pipel.c

read() blocks until data is available

```

```

write() blocks if pipe buffer is full

```

```

st pipe file descriptors are inherited across fork

so pipes can be used to communicate between processes

example: pipe2.c

for many programs, just like file I/O, so pipes work for stdin/stdout

* for 1s | wc -1, shell must:

- create a pipe

- fork

- set up fd 1 to be the pipe write FD

- exec 1s

- set up wc's fd 0 to be pipe read FD

- exec wc

- wait for wc

[diagram: sh parent, 1s child, wc child, stdin/out for each]

case '|' in sh.c

note: sh close()es unused FDs

so exit of writer produces EOF at reader

```

st you'll implement pieces of a shell in an upcoming homework

# 6.828 Lecture Notes: x86 and PC architecture

## **Outline**

- PC architecture

- x86 instruction set

- gcc calling conventions

- PC emulation

### PC architecture

- A full PC has:

- an x86 CPU with registers, execution unit, and memory management

- o CPU chip pins include address and data signals

- memory

- disk

- keyboard

- display

- o other resources: BIOS ROM, clock, ...

- We will start with the original 16-bit 8086 CPU (1978)

- CPU runs instructions:

```

for(;;){

run next instruction

}

```

- Needs work space: registers

- o four 16-bit data registers: AX, BX, CX, DX

- each in two 8-bit halves, e.g. AH and AL

- very fast, very few

- More work space: memory

- CPU sends out address on address lines (wires, one bit per wire)

- Data comes back on data lines

- o or data is written to data lines

- Add address registers: pointers into memory

- SP stack pointer

- BP frame base pointer

- SI source index

- DI destination index

- Instructions are in memory too!

- IP instruction pointer (PC on PDP-11, everything else)

- increment after running each instruction

- can be modified by CALL, RET, JMP, conditional jumps

- Want conditional jumps

- FLAGS various condition codes

- whether last arithmetic operation overflowed

- ... was positive/negative

- ... was [not] zero

- ... carry/borrow on add/subtract

- ... etc.

- whether interrupts are enabled

- direction of data copy instructions

- JP, JN, J[N]Z, J[N]C, J[N]O ...

- Still not interesting need I/O to interact with outside world

- Original PC architecture: use dedicated I/O space

- Works same as memory accesses but set I/O signal

- Only 1024 I/O addresses

- Accessed with special instructions (IN, OUT)

- Example: write a byte to line printer:

- Memory-Mapped I/O

- Use normal physical memory addresses

- Gets around limited size of I/O address space

- No need for special instructions

- System controller routes to appropriate device

- Works like "magic" memory:

- Addressed and accessed like memory, but ...

- ... does not *behave* like memory!

- Reads and writes can have "side effects"

- Read results can change due to external events

- What if we want to use more than 2^16 bytes of memory?

- 8086 has 20-bit physical addresses, can have 1 Meg RAM

- o the extra four bits usually come from a 16-bit "segment register":

- CS code segment, for fetches via IP

- SS stack segment, for load/store via SP and BP

- DS data segment, for load/store via other registers

- ES another data segment, destination for string operations

- virtual to physical translation: pa = va + seg\*16

- e.g. set CS = 4096 to execute starting at 65536

- o tricky: can't use the 16-bit address of a stack variable as a pointer

- o a far pointer includes full segment:offset (16 + 16 bits)

- tricky: pointer arithmetic and array indexing across segment boundaries

- But 8086's 16-bit addresses and data were still painfully small

- o 80386 added support for 32-bit data and addresses (1985)

- o boots in 16-bit mode, boot. S switches to 32-bit mode

- registers are 32 bits wide, called EAX rather than AX

- operands and addresses that were 16-bit became 32-bit in 32-bit mode, e.g.

ADD does 32-bit arithmetic

- prefixes 0x66/0x67 toggle between 16-bit and 32-bit operands and addresses: in 32-bit mode, MOVW is expressed as 0x66 MOVW

- o the .code32 in boot.S tells assembler to generate 0x66 for e.g. MOVW

- 80386 also changed segments and added paged memory...

- Example instruction encoding

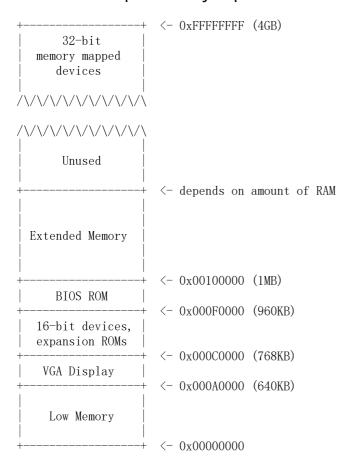

## x86 Physical Memory Map

- The physical address space mostly looks like ordinary RAM

- Except some low-memory addresses actually refer to other things

- Writes to VGA memory appear on the screen

- Reset or power-on jumps to ROM at 0xfffffff0 (so must be ROM at top...)

## x86 Instruction Set

- Intel syntax: op dst, src (Intel manuals!)

- AT&T (gcc/gas) syntax: op src, dst (labs, xv6)

- uses b, w, I suffix on instructions to specify size of operands

- Operands are registers, constant, memory via register, memory via constant

- Examples:

AT&T syntax

movl %eax, %edx

edx = eax;

register mode

movl \$0x123, %edx

edx = 0x123;

immediate

movl 0x123, %edx

edx = \*(int32\_t\*)0x123;

direct

movl (%ebx), %edx

edx = \*(int32\_t\*)ebx;

indirect

movl 4(%ebx), %edx

edx = \*(int32\_t\*)(ebx+4);

displaced

- Instruction classes

- o data movement: MOV, PUSH, POP, ...

- o arithmetic: TEST, SHL, ADD, AND, ...

- ∘ i/o: IN, OUT, ...

- control: JMP, JZ, JNZ, CALL, RET

- o string: REP MOVSB, ...

- system: IRET, INT

- Intel architecture manual Volume 2 is *the* reference

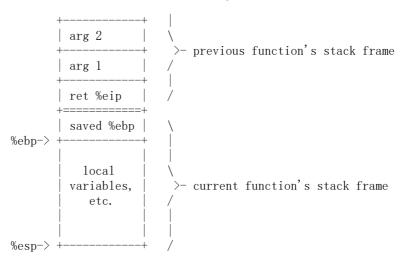

## gcc x86 calling conventions

• x86 dictates that stack grows down:

#### **Example instruction** What it does

pushl %eax

subl \$4, %esp movl %eax, (%esp)

popl %eax

movl (%esp), %eax addl \$4, %esp

call 0x12345

pushl %eip (\*) movl \$0x12345, %eip (\*)

ret

popl %eip (\*)

- (\*) Not real instructions

- GCC dictates how the stack is used. Contract between caller and callee on x86:

- o at entry to a function (i.e. just after call):

- %eip points at first instruction of function

- %esp+4 points at first argument

- %esp points at return address

- o after ret instruction:

- %eip contains return address

- %esp points at arguments pushed by caller

- called function may have trashed arguments

- %eax (and %edx, if return type is 64-bit) contains return value (or trash if function is void)

- %eax, %edx (above), and %ecx may be trashed

- %ebp, %ebx, %esi, %edi must contain contents from time of call

- Terminology:

- %eax, %ecx, %edx are "caller save" registers

- %ebp, %ebx, %esi, %edi are "callee save" registers

- Functions can do anything that doesn't violate contract. By convention, GCC does more:

- o each function has a stack frame marked by %ebp, %esp

- %esp can move to make stack frame bigger, smaller

- o %ebp points at saved %ebp from previous function, chain to walk stack

- function prologue:

```

push1 %ebp

mov1 %esp, %ebp

```

or

enter \$0, \$0

enter usually not used: 4 bytes vs 3 for pushl+movl, not on hardware fast-path anymore

o function epilogue can easily find return EIP on stack:

```

movl %ebp, %esp

popl %ebp

```

or

1eave

leave used often because it's 1 byte, vs 3 for movl+popl

- Big example:

- o C code

```

int main(void) { return f(8)+1; }

int f(int x) { return g(x); }

int g(int x) { return x+3; }

```

o assembler

```

_main: prologue

pushl %ebp

```

```

mov1 %esp, %ebp

body

push1 $8

call _f

addl $1, %eax

epilogue

mov1 %ebp, %esp

popl %ebp

ret

_f:

prologue

pushl %ebp

mov1 %esp, %ebp

body

push1 8(%esp)

call _g

epilogue

mov1 %ebp, %esp

pop1 %ebp

ret

_g:

prologue

pushl %ebp

mov1 %esp, %ebp

save %ebx

pushl %ebx

body

mov1 8(%ebp), %ebx

add1 $3, %ebx

mov1 %ebx, %eax

restore %ebx

popl %ebx

epilogue

mov1 %ebp, %esp

popl %ebp

```

• Super-small \_g:

```

_g:

mov1 4(%esp), %eax

add1 $3, %eax

ret

```

- Shortest f?

- Compiling, linking, loading:

- Preprocessor takes C source code (ASCII text), expands #include etc, produces C source code

- Compiler takes C source code (ASCII text), produces assembly language (also ASCII text)

- Assembler takes assembly language (ASCII text), produces . file (binary, machine-readable!)

- Linker takes multiple '. o's, produces a single program image (binary)

- o Loader loads the program image into memory at run-time and starts it executing

## **PC** emulation

- The Bochs emulator works by

- o doing exactly what a real PC would do,

- only implemented in software rather than hardware!

- Runs as a normal process in a "host" operating system (e.g., Linux)

- Uses normal process storage to hold emulated hardware state: e.g.,

- Stores emulated CPU registers in global variables

```

int32_t regs[8];

#define REG_EAX 1;

#define REG_EBX 2;

#define REG_ECX 3;

...

int32_t eip;

int16_t segregs[4];

```

Stores emulated physical memory in Boch's memory

```

char mem[256*1024*1024];

```

• Execute instructions by simulating them in a loop:

```

for (;;) {

read instruction();

switch (decode instruction opcode()) {

case OPCODE ADD:

int src = decode_src_reg();

int dst = decode dst reg();

regs[dst] = regs[dst] + regs[src];

break;

case OPCODE SUB:

int src = decode_src_reg();

int dst = decode_dst_reg();

regs[dst] = regs[dst] - regs[src];

break;

. . .

eip += instruction_length;

}

```

• Simulate PC's physical memory map by decoding emulated "physical" addresses just like a PC would:

```

#define KB

1024

#define MB

1024*1024

#define LOW MEMORY

640*KB

#define EXT MEMORY

uint8 t low mem[LOW MEMORY];

uint8 t ext mem[EXT MEMORY];

uint8_t bios_rom[64*KB];

uint8 t read byte(uint32 t phys addr) {

if (phys_addr < LOW_MEMORY)

return low mem[phys addr];

else if (phys_addr >= 960*KB \&\& phys addr < 1*MB)

return rom_bios[phys_addr - 960*KB];

else if (phys_addr \geq 1*MB && phys_addr \leq 1*MB+EXT_MEMORY) {

return ext mem[phys addr-1*MB];

else \dots \\

void write_byte(uint32_t phys_addr, uint8_t val) {

if (phys_addr < LOW MEMORY)

low mem[phys addr] = val;

```

- Simulate I/O devices, etc., by detecting accesses to "special" memory and I/O space and emulating the correct behavior: e.g.,

- Reads/writes to emulated hard disk transformed into reads/writes of a file on the host system

- Writes to emulated VGA display hardware transformed into drawing into an X window

- Reads from emulated PC keyboard transformed into reads from X input event queue

```

Lecture Topic:

kernel system call API

both details and design

illustrate via shell and homework 2

Overview Diagram

user / kernel

process = address space + thread(s)

app -> printf() -> write() -> SYSTEM CALL -> sys write() -> ...

user-level libraries are app's private business

kernel internal functions are not callable by user

xv6 has a few dozen system calls; Linux a few hundred

details today are mostly about UNIX system-call API

basis for xv6, Linux, OSX, POSIX standard, &c

jos has very different system-calls; you'll build UNIX calls over jos

Homework solution

* Let's review Homework 2 (sh.c)

* exec

why two execv() arguments?

what happens to the arguments?

what happens when exec'd process finishes?

can execv() return?

how is the shell able to continue after the command finishes?

* redirect

how does exec'd process learn about redirects? [kernel fd tables]

does the redirect (or error exit) affect the main shell?

* pipe

1s | wc -1

what if 1s produces output faster than wc consumes it?

what if 1s is slower than wc?

how does each command decide when to exit?

what if reader didn't close the write end? [try it]

what if writer didn't close the read end?

how does the kernel know when to free the pipe buffer?

* how does the shell know a pipeline is finished?

e.g. ls | sort | tail -1

* what's the tree of processes?

sh parses as: ls | (sort | tail -1)

sh

sh1

1s

sh2

sort

tail

* does the shell need to fork so many times?

- what if sh didn't fork for pcmd->left? [try it]

i.e. called runcmd() without forking?

- what if sh didn't fork for pcmd->right? [try it]

would user-visible behavior change?

sleep 10 | echo hi

* why wait() for pipe processes only after both are started?

what if sh wait()ed for pcmd->left before 2nd fork? [try it]

1s | wc -1

cat < big | wc -1

* the point: the system calls can be combined in many ways

to obtain different behaviors.

Let's look at the challenge problems

* How to implement sequencing with ";"?

gcc sh.c; ./a.out

echo a ; echo b

```

```

why wait() before scmd->right? [try it]

* How to implement "%"?

$ sleep 5 &

$ wait

the implementation of & and wait is in main -- why?

What if a background process exits while sh waits for a foreground process?

* How to implement nesting?

$ (echo a; echo b) | wc -1

my (...) implementation is only in sh's parser, not runcmd()

it's neat that sh pipe code doesn't have to know it's applying to a sequence

* How do these differ?

echo a > x; echo b > x

(echo a ; echo b) > x

what's the mechanism that avoids overwriting?

UNIX system call observations

* The fork/exec split looks wasteful -- fork() copies mem, exec() discards.

why not e.g. pid = forkexec(path, argv, fd0, fd1)?

the fork/exec split is useful:

fork(); I/O redirection; exec()

or fork(); complex nested command; exit.

as in (cmd1; cmd2) | cmd3

fork() alone: parallel processing

exec() alone: /bin/login ... exec("/bin/sh")

fork is cheap for small programs — on my machine:

fork+exec takes 400 microseconds (2500 / second)

fork alone takes 80 microseconds (12000 / second)

some tricks are involved -- you'll implement them in jos!

* The file descriptor design:

* FDs are a level of indirection

- a process's real I/O environment is hidden in the kernel

- preserved over fork and exec

- separates I/O setup from use

- imagine writefile(filename, offset, buf size)

* FDs help make programs more general purpose: don't need special cases for

files vs console vs pipe

* Philosophy: small set of conceptually simple calls that combine well

e.g. fork(), open(), dup(), exec()

command-line design has a similar approach

1s | wc -1

* Why must kernel support pipes -- why not have sh simulate them, e.g.

ls > tempfile ; wc -1 < tempfile

* System call interface simple, just ints and char buffers. why not have open()

return a pointer reference to a kernel file object?

* The core UNIX system calls are ancient; have they held up well?

yes; very successful

and evolved well over many years

history: design caters to command-line and s/w development

system call interface is easy for programmers to use

command-line users like named files, pipelines, &c

important for development, debugging, server maintenance

but the UNIX ideas are not perfect:

programmer convenience is often not very valuable for system-call API

programmers use libraries e.g. Python that hide sys call details

apps may have little to do with files &c, e.g. on smartphone

some UNIX abstractions aren't very efficient

fork() for multi-GB process is very slow

FDs hide specifics that may be important

e.g. block size for on-disk files

e.g. timing and size of network messages

```

so there has been lots of work on alternate plans sometimes new system calls and abstractions for existing UNIX-like kernels sometimes entirely new approaches to what a kernel should do ask "why this way? wouldn't design X be better?"

#### OS organization

- \* How to implement a system-call interface?

- \* Why not just a library?

I.e. no kernel, just run app+library directly on the hardware.

flexible: apps can bypass library if it's not right

apps can directly interact with hardware

a library is OK for a single-purpose device

but what if the computer is used for multiple activities?

- \* Key requirements for kernels: isolation multiplexing interaction

- \* helpful approach: abstract resources rather than raw hardware

File system, not raw disk

Processes, not raw CPU/memory

TCP, not ethernet packets

abstractions often ease isolation, multiplexing and interaction

also more convenient and portable

- \* Start with isolation since that's often the most constraining requirement.

- \* Isolation goals:

apps cannot directly interact with hardware

apps cannot harm operating system

apps cannot directly affect each other

apps can only interact with world via the OS interface

- \* Processors provide mechanisms that help with isolation

- \* Hardware provides user mode and kernel mode

- some instructions can only be executed in kernel mode device access, processor configuration, isolation mechanisms

- st Hardware forbids apps from executing privileged instructions

- instead traps to kernel mode

- kernel can clean up (e.g., kill the process)

- \* Hardware lets kernel mode configure various constraints on user mode most critical: page tables to limit user s/w to its own address space

- \* Kernel builds on hardware isolation mechanisms

- \* Operating system runs in kernel mode

- kernel is a big program services: processes, file system, net

services: processes, file system, net low-level: devices, virtual memory all of kernel runs with full hardware privilege (convenient)

- \* Applications run in user mode

- kernel sets up per-process isolated address space

- system calls switch between user and kernel mode the application executes a special instruction to enter kernel hardware switches to kernel mode but only at an entry point specified by the kernel

- \* What to put in the kernel?

- \* xv6 follows a traditional design: all of the OS runs in kernel mode

- one big program with file system, drivers, &c

- this design is called a monolithic kernel

- kernel interface == system call interface

- good: easy for subsystems to cooperate one cache shared by file system and virtual memory

bad: interactions are complex leads to bugs no isolation within kernel

#### \* microkernel design

- many OS services run as ordinary user programs file system in a file server

- kernel implements minimal mechanism to run services in user space processes with memory inter-process communication (IPC)

- kernel interface != system call interface

- good: more isolation

- bad: may be hard to get good performance

- \* exokernel: no abstractions

apps can use hardware semi-directly, but O/S isolates e.g. app can read/write own page table, but O/S audits e.g. app can read/write disk blocks, but O/S tracks block owners good: more flexibility for demanding applications jos will be a mix of microkernel and exokernel

\* Can one have process isolation WITHOUT h/w-supported kernel/user mode? yes!

see Singularity O/S, later in semester but h/w user/kernel mode is the most popular plan

Next lecture: x86 hardware isolation mechanisms and xv6's use of them

```

Today:

user/kernel isolation

xv6 system call as case study

* How to choose overall form for a kernel?

many possible answers!

one extreme:

just a library of device drivers, linked w/ app

run application directly on hardware

fast and flexible for single-purpose devices

but usually multiple tasks on a computer

* Multiple tasks drive the key requirements:

multiplexing

isolation

interaction

* helpful approach: abstract resources rather than raw hardware

File system, not raw disk

Processes, not raw CPU/memory

TCP connections, not ethernet packets

abstractions are often easier to isolate and share

e.g. programs see a private CPU, needn't think about multiplexing

also more convenient and portable

* Isolation is often the most constraining requirement.

* What is isolation?

enforced separation to contain effects of failures

the process is the usual unit of isolation

prevent process X from wrecking or spying on process Y

r/w memory, use 100% of CPU, change FDs, &c

prevent a process from interfering with the operating system

in the face of malice as well as bugs

a bad process may try to trick the h/w or kernel

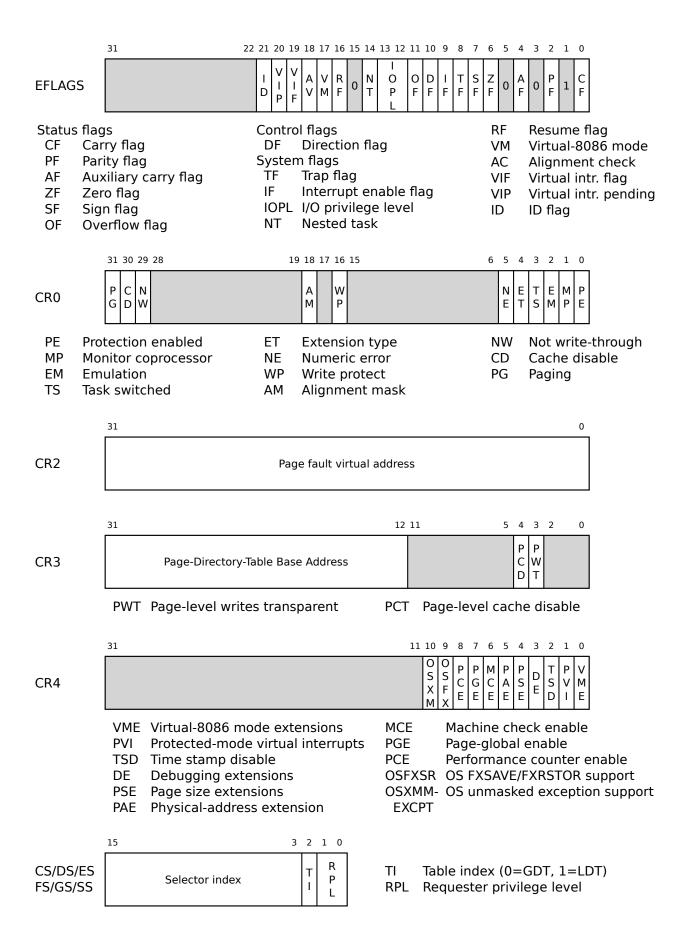

* the kernel uses hardware mechanisms as part of process isolation:

user/kernel mode flag

address spaces

timeslicing

system call interface

* the hardware user/kernel mode flag

controls whether instructions can access privileged h/w

called CPL on the x86, bottom two bits of %cs register

CPL=0 -- kernel mode -- privileged

CPL=3 -- user mode -- no privilege

x86 CPL protects many processor registers relevant to isolation

I/O port accesses

control register accesses (eflags, %cs4, ...)

including %cs itself

affects memory access permissions, but indirectly

the kernel must set all this up correctly

every serious microprocessor has some kind of user/kernel flag

* how to do a system call -- switching CPL

Q: would this be an OK design for user programs to make a system call:

set CPL=0

jmp sys open

bad: user-specified instructions with CPL=0

Q: how about a combined instruction that sets CPL=0,

but *requires* an immediate jump to someplace in the kernel?

bad: user might jump somewhere awkward in the kernel

the x86 answer:

there are only a few permissible kernel entry points ("vectors")

INT instruction sets CPL=0 and jumps to an entry point

but user code can't otherwise modify CPL or jump anywhere else in kernel

```

```

system call return sets CPL=3 before returning to user code

also a combined instruction (can't separately set CPL and jmp)

* the result: well-defined notion of user vs kernel

either CPL=3 and executing user code

or CPL=0 and executing from entry point in kernel code

CPL=0 and executing user code

CPL=0 and executing anywhere in kernel the user pleases

* how to isolate process memory?

idea: "address space"

give each process some memory it can access

for its code, variables, heap, stack

prevent it from accessing other memory (kernel or other processes)

* how to create isolated address spaces?

xv6 uses x86 "paging hardware" in the memory management unit (MMU)

MMU translates (or "maps") every address issued by program

CPU -> MMU -> RAM

pagetable

VA -> PA

MMU translates all memory references: user and kernel, instructions and data

instructions use only VAs, never PAs

kernel sets up a different page table for each process

each process's page table allows access only to that process's RAM

### Let's look at how xv6 system calls are implemented

xv6 process/stack diagram:

user process; kernel thread

user stack; kernel stack

two mechanisms:

switch between user/kernel

switch between kernel threads

trap frame

kernel function calls...

struct context

* simplified xv6 user/kernel virtual address-space setup

FFFFFFFF:

80000000: kernel

user stack

user data

00000000: user instructions

kernel configures MMU to give user code access only to lower half

separate address space for each process

but kernel (high) mappings are the same for every process

system call starting point:

executing in user space, sh writing its prompt

sh. asm, write() library function

break *0xb90

x/3i 0xb8b

0x10 in eax is the system call number for write

cs=0x1b, B=1011 -- CPL=3 \Rightarrow user mode

esp and eip are low addresses -- user virtual addresses

x/4x \$esp

ccl is return address -- in printf

2 is fd

0x3f7a is buffer on the stack

1 is count

i.e. write(2, 0x3f7a, 1)

x/c 0x3f7a

```

INT instruction, kernel entry

```

stepi

info reg

cs=0x8 -- CPL=3 => kernel mode

note INT changed eip and esp to high kernel addresses

where is eip?

at a kernel-supplied vector -- only place user can go

so user program can't jump to random places in kernel with CPL=0

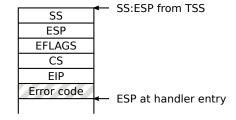

x/6wx $esp

INT saved a few user registers

err, eip, cs, eflags, esp, ss

why did INT save just these registers?

they are the ones that INT overwrites

what INT did:

switched to current process's kernel stack

saved some user registers on kernel stack

set CPL=0

start executing at kernel-supplied "vector"

where did esp come from?

kernel told h/w what kernel stack to use when creating process

Q: why does INT bother saving the user state?

how much state should be saved?

transparency vs speed

saving the rest of the user registers on the kernel stack

trapasm. S alltraps

pushal pushes 8 registers: eax .. edi

x/19x \$esp

19 words at top of kernel stack:

SS

esp

eflags

CS

-- INT saved from here up

trapno

ds

es

fs

gs

eax..edi

will eventually be restored, when system call returns

meanwhile the kernel C code sometimes needs to read/write saved values

struct trapframe in x86.h

Q: why are user registers saved on the kernel stack?

why not save them on the user stack?

entering kernel C code

the push! %esp creates an argument for trap(struct trapframe *tf)

now we're in trap() in trap.c

print tf

print *tf

kernel system call handling

device interrupts and faults also enter trap()

trapno == T SYSCALL

myproc()

struct proc in proc.h

myproc()->tf -- so syscall() can get at call # and arguments

syscall() in syscall.c

looks at tf->eax to find out which system call

SYS write in syscalls[] maps to sys write

sys write() in sysfile.c

arg*() read write(fd, buf, n) arguments from the user stack

argint() in syscall.c

proc \rightarrow tf \rightarrow esp + xxx

```

```

syscall() sets tf->eax to return value

back to trap()

finish -- returns to trapasm. S

info reg -- still in kernel, registers overwritten by kernel code

stepi to iret

info reg

most registers hold restored user values

eax has write() return value of 1

esp, eip, cs still have kernel values

x/5x \$esp

saved user state: eip, cs, eflags, esp, ss

IRET pops those user registers from the stack

and thereby re-enters user space with CPL=3

Q: do we really need IRET?

could we use ordinary instructions to restore the registers?

could IRET be simpler?

back to user space

stepi

info reg

*** fork()

let's look at how fork() sets up a new process

in particular, how to get the new process into user space the first time?

the idea:

fork() fakes a kernel stack that *looks* like it's about to return from trap()

with a faked trapframe at the top

child starts executing in the kernel -- at a function return instruction

alltraps "restores" faked saved registers

starts executing the child for the first time

note there are two separate actions:

create a new process

execute the new process

break fork

where

fork() in proc. c

allocproc()

look at proc[] at start of proc.c

focus on initial content of p->kstack

space for trap frame (will be a copy of parent's)

fake saved EIP that points to trapret in trapasm.S

kernel stack space for a "context"

contains *kernel* registers

to be restored when switching to child's kernel thread

the p->context->eip = forkret sets up where child starts in the kernel

basically just a fuction call instruction

back to fork()

(remember we're still executing as the parent)

allocate physical memory and a page table

copy parent's memory to child

copy trapframe

tf->eax = 0 -- this will the child's return value from fork():w

print *np

print *np->tf

print *np->context

x/25x np->context

state = RUNNABLE -- now we are done

the new process's kernel stack:

trapframe -- copy of parent, but eax=0

```

```

trapret's address

context

eip = forkret

```

break forkret x/20x \$esp next finish (now in trapret in tramasm.S) at b6a in sh.S info reg and eax is zero — it's the child

```

6.828 2016 Lecture 6: Virtual Memory

* plan:

address spaces

paging hardware

xv6 VM code

case study

finish lec 5

homework sol

## Virtual memory overview

* today's problem:

[user/kernel diagram]

[memory view: diagram with user processes and kernel in memory]

suppose the shell has a bug:

sometimes it writes to a random memory address

how can we keep it from wrecking the kernel?

and from wrecking other processes?

* we want isolated address spaces

each process has its own memory

it can read and write its own memory

it cannot read or write anything else

challenge:

how to multiplex several memories over one physical memory?

while maintaining isolation between memories

* xv6 and JOS uses x86's paging hardware to implement AS's

ask questions! this material is important

* paging provides a level of indirection for addressing

CPU -> MMU -> RAM

VA

s/w can only ld/st to virtual addresses, not physical

kernel tells MMU how to map each virtual address to a physical address

MMU essentially has a table, indexed by va, yielding pa

called a "page table"

MMU can restrict what virtual addresses user code can use

* x86 maps 4-KB "pages"

and aligned -- start on 4 KB boundaries

thus page table index is top 20 bits of VA

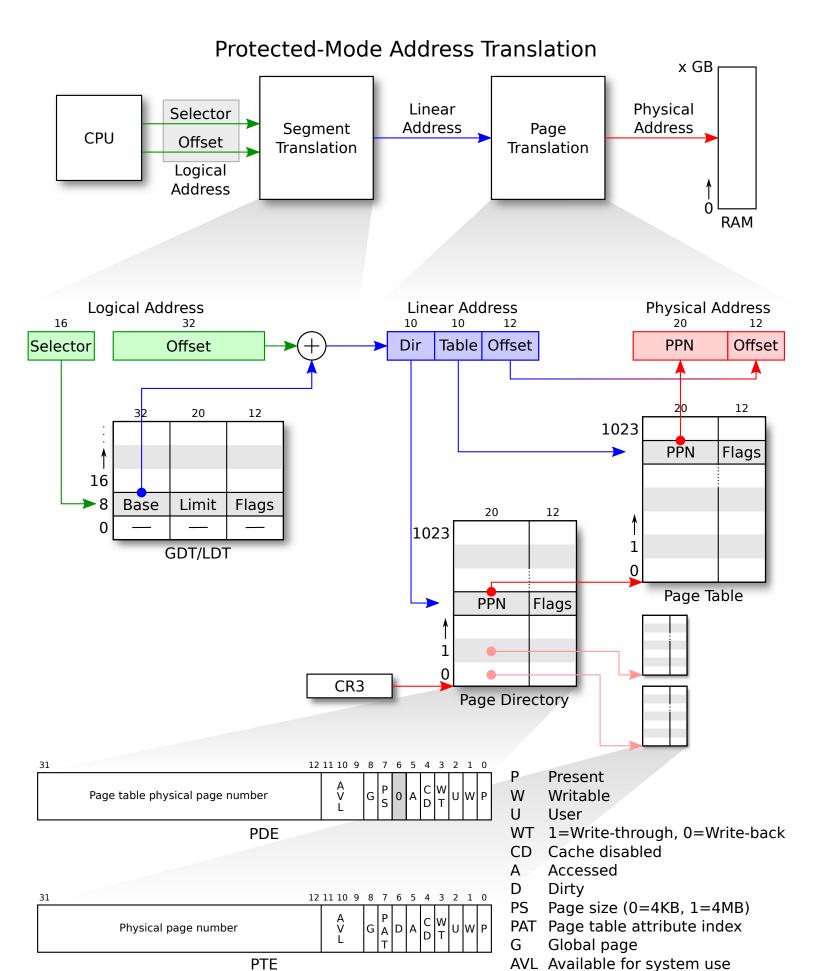

* what is in a page table entry (PTE)?

see [handout] (x86 translation and registers.pdf)

top 20 bits are top 20 bits of physical address

"physical page number"

MMU replaces top 20 of VA with PPN

low 12 bits are flags

Present, Writeable, &c

* where is the page table stored?

in RAM -- MMU loads (and stores) PTEs

o/s can read/write PTEs

* would it be reasonable for page table to just be an array of PTEs?

how big is it?

2<sup>20</sup> is a million

32 bits per entry

4 MB for a full page table -- pretty big on early machines

would waste lots of memory for small programs!

you only need mappings for a few hundred pages

so the rest of the million entries would be there but not needed

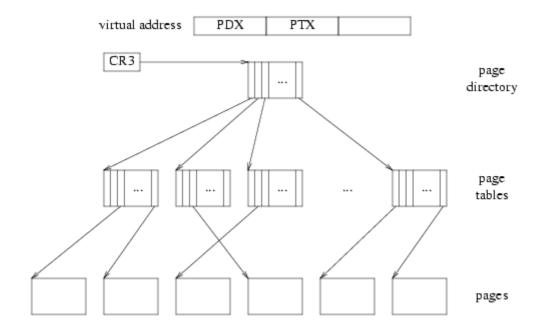

* x86 uses a "two-level page table" to save space

diagram

pages of PTEs in RAM

```

```

page directory (PD) in RAM

PDE also contains 20-bit PPN -- of a page of 1024 PTEs

1024 PDEs point to PTE pages

each PTE page has 1024 PTEs -- so 1024*1024 PTEs in total

PD entries can be invalid

those PTE pages need not exist

so a page table for a small address space can be small

* how does the mmu know where the page table is located in RAM?

%cr3 holds phys address of PD

PD holds phys address of PTE pages

they can be anywhere in RAM -- need not be contiguous

* how does x86 paging hardware translate a va?

need to find the right PTE

%cr3 points to PA of PD

top 10 bits index PD to get PA of PT

next 10 bits index PT to get PTE

PPN from PTE + 1ow-12 from VA

* flags in PTE

P, W, U

xv6 uses U to forbid user from using kernel memory

* what if P bit not set? or store and W bit not set?

"page fault'

CPU saves registers, forces transfer to kernel

trap. c in xv6 source

kernel can just produce error, kill process

or kernel can install a PTE, resume the process

e.g. after loading the page of memory from disk

* Q: why mapping rather than e.g. base/bound?

indirection allows paging h/w to solve many problems

e.g. avoids fragmentation

e.g. copy-on-write fork

e.g. lazy allocation (home work for next lecture)

many more techniques

topic of next lecture

* Q: why use virtual memory in kernel?

it is clearly good to have page tables for user processes

but why have a page table for the kernel?

could the kernel run with using only physical addresses?

top-level answer: yes

Singularity is an example kernel using phys addresses

but, most standard kernels do use virtual addresses?

why do standard kernels do so?

some reasons are lame, some are better, none are fundamental

- the hardware makes it difficult to turn it off

e.g. on entering a system call, one would have to disable VM

- it can be convenient for the kernel to use user addresses

e.g. a user address passed to a system call

but, probably a bad idea: poor isolation between kernel/application

- convenient if addresses are contiguous

say kernel has both 4Kbyte objects and 64Kbyte objects

without page tables, we can easily have memory fragmentation

e.g., allocate 64K, allocate 4Kbyte, free the 64K, allocate 4Kbyte from the 64Kbyte

now a new 64Kbyte object cannot use the free 60Kbyte.

- the kernel must run of a wide range of hardware

they may have different physical memory layouts

## Case study: xv6 use of the x86 paging hardware

* big picture of an xv6 address space -- one per process

[diagram]

0x00000000:0x80000000 -- user addresses below KERNBASE

0x80000000:0x80100000 -- map low 1MB devices (for kernel)

```

-- kernel instructions/data

0x80100000:?

```

0xFE000000:0x00000000 -- more memory-mapped devices

* where does xv6 map these regions, in phys mem?

diagram from book: xv6-layout.eps

note double-mapping of user pages

* each process has its own address space

and its own page table

all processes have the same kernel (high memory) mappings

kernel switches page tables (i.e. sets %cr3) when switching processes

* Q: why this address space arrangement?

user virtual addresses start at zero

of course user va 0 maps to different pa for each process

2GB for user heap to grow contiguously

but needn't have contiguous phys mem -- no fragmentation problem

both kernel and user mapped -- easy to switch for syscall, interrupt

kernel mapped at same place for all processes

eases switching between processes

easy for kernel to r/w user memory

using user addresses, e.g. sys call arguments

easy for kernel to r/w physical memory

pa x mapped at va x+0x80000000

we'll see this soon while manipulating page tables

* Q: what's the largest process this scheme can accommodate?

* Q: could we increase that by increasing/decreasing 0x80000000?

* Q: does the kernel have to map all of phys mem into its virtual address space?

* let's look at some xv6 virtual memory code

terminology: virtual memory == address space / translation

will help you w. next homework and labs

<!---

start where Robert left off: first process

setup: CPUS=1, turn-off interrupts in lapic.c

b proc. c:297

р *р

Q: are these addresses virtual addresses

break into gemu: info pg (modified 6.828 gemu)

step into switchuvm

x/1024x p->pgdir

what is 0x0dfbc007?

(pde; see handout)

what is 0x0dfbc000?

what is 0x0dfbc000 + 0x8000000

what is there? (pte)

what is at 0x8dfbd000?

x x/i 0x8dfbd000 (first word of initcode.asm)

step passed 1cr3

qemu: info pg

-->

* where did this pgdir get setup?

look at vm.c: setupkvm and inituvm

```

:0x8E000000 -- 224 MB of DRAM mapped here

```

* mappages() in vm.c

arguments are PD, va, size, pa, perm

adds mappings from a range of va's to corresponding pa's

rounds b/c some uses pass in non-page-aligned addresses

for each page-aligned address in the range

call walkpgdir to find address of PTE

need the PTE's address (not just content) b/c we want to modify

put the desired pa into the PTE

mark PTE as valid w/ PTE_P

* diagram of PD &c, as following steps build it

* walkpgdir() in vm.c

mimics how the paging h/w finds the PTE for an address

refer to the handout

PDX extracts top ten bits

&pgdir[PDX(va)] is the address of the relevant PDE

now *pde is the PDE

if PTE P

the relevant page-table page already exists

PTE_ADDR extracts the PPN from the PDE

p2v() adds 0x80000000, since PTE holds physical address

if not PTE P

alloc a page-table page

fill in PDE with PPN -- thus v2p

now the PTE we want is in the page-table page

at offset PTX(va)

which is 2nd 10 bits of va

<!--

finish starting the first user process

return to gdb

(draw picture of kstack)

p/x p\rightarrow tf

p/x *p \rightarrow tf

p /x p→context

p /x p→context

b *0x0

swtch

x/8x $esp

forkret

x/19x \$esp

info reg

step till user space:

x/i 0x0

step through use code

trap into kernel

x/19x \$esp

-->

* tracing and date system call

<!-- homework

syscall trace

syscall.c (HWSYS)

return value in eax

use STAB for printing out names

date

usys. S

```

```

syscall.c (HWDATE)

argptr

* a process calls sbrk(n) to ask for n more bytes of heap memory

malloc() uses sbrk()

each process has a size

kernel adds new memory at process's end, increases size

sbrk() allocates physical memory (RAM)

maps it into the process's page table

returns the starting address of the new memory

* sys_sbrk() in sysproc.c

<!---

trace sbrk from user space

just run ls (or any other cmd from shell)

the new process forked by shell calls malloc for execomd structure

malloc.c calls sbrk

* growproc() in proc.c

proc->sz is the process's current size

allocuvm() does most of the work

switchuvm sets %cr3 with new page table

also flushes some MMU caches so it will see new PTEs

* allocuvm() in vm.c

why if (newsz >= KERNBASE) ?

why PGROUNDUP?

arguments to mappages()...

```

**PTE**

```

* plan: cool things you can do with vm

- Better performance/efficiency

e.g., one zero-filled page

e.g., copy-on-write fork

- New features

e.g., memory-mapped files

- JOS and VM

- This lecture may generate ideas for last lab (final project)

isolation: picture with walls

return user space, until we hit first system call

then switch to date homework

date system call homework

point out some of the walls:

U/K bit

user cannot execute privileged instructions

user enter kernel only through system calls

only kernel can load cr3

Page tables

no U bit on kernel pages

But sharing too:

Kernel can read/write user memory

Requires kernel checks arguments of system call

-->

* virtual memory: several views

* primary purpose: isolation

each process has its own address space

* Virtual memory provides a level-of-indirection

provides kernel with opportunity to do cool stuff

* lazy/on-demand page allocation

* sbrk() is old fashioned;

it asks application to "predict" how much memory they need

difficult for applications to predict how much memory they need in advance

sbrk allocates memory that may never be used.

* moderns OSes allocate memory lazily

allocate physical memory when application needs it

* HW solution

<!---

draw xv6 user-part of address space

demo solution; breakpoint right before mappages in trap.c

explain page faults

-->

<!--

xv6 memlayout discussion

user virtual addresses start at zero

of course user va 0 maps to different pa for each process

2GB for user heap to grow contiguously

but needn't have contiguous phys mem -- no fragmentation problem

both kernel and user mapped -- easy to switch for syscall, interrupt

kernel mapped at same place for all processes

eases switching between processes

easy for kernel to r/w user memory

using user addresses, e.g. sys call arguments

easy for kernel to r/w physical memory

pa x mapped at va x+0x80000000

we'll see this soon while manipulating page tables

lame part: user stack

also, initcode and date (different AS layout)

```

6.828 2016 Lecture 7: using virtual memory

```

but convenient to check if an address is valid (va < p->size)

why is kernel using vm?

* Step back: class perspective

- There is no one best way to design an OS

Many OSes use VM, but you don't have to

Xv6 and JOS present examples of OS designs

They lack many features of sophisticated designs

In fact, they are pretty lame compared to a real OS

Yet, still quite complex

- Our goal: to teach you the key ideas so that you can extrapolate

Xv6 and JOS are minimal design to expose key ideas

You should be able to make them better

You should be able to dive into Linux and find your way

* guard page to protect against stack overflow

* put a non-mapped page below user stack

if stack overflows, application will see page fault

* allocate more stack when application runs off stack into guard page

<!--

draw xv6 user-part of address space

compile with -0 so the compiler doesn't optimize the tail recursion

demo stackoverflow

set breakpoint at g

run stackoverflow

look at $esp

look at pg info at qemu console

note page has no U bit

* one zero-filled page

* kernel often fills a page with zeros

* idea: memset *one* page with zeros

map that page copy-on-write when kernel needs zero-filled page

on write make copy of page and map it read/write in app address space

* share kernel page tables in xv6

* observation:

kvmalloc() allocates new pages for kernel page table for each process

but all processes have the same kernel page table

* idea: modify kvmalloc()/freevm() to share kernel page table

<!--

demo HWKVM

-->

* copy-on-write fork

* observation:

xv6 fork copies all pages from parent (see fork())

but fork is often immediately followed by exec

* idea: share address space between parent and child

modify fork() to map pages copy-on-write (use extra available system bits in PTEs and PDEs)

on page fault, make copy of page and map it read/write

* demand paging

* observation: exec loads the complete file into memory (see exec.c)

expensive: takes time to do so (e.g., file is stored on a slow disk)

unnecessary: maybe not the whole file will be used

* idea: load pages from the file on demand

allocate page table entries, but mark them on-demand

on fault, read the page in from the file and update page table entry

* challenge: file larger than physical memory (see next idea)

* use virtual memory larger than physical memory

* observation: application may need more memory than there is physical memory

* idea: store less-frequently used parts of the address space on disk

page-in and page-out pages of the address address space transparently

```

\* works when working sets fits in physical memory

```

* memory-mapped files

oldsymbol{*} idea: allow access to files using load and store

can easily read and writes part of a file

e.g., don't have to change offset using lseek system call

* page-in pages of a file on demand

when memory is full, page-out pages of a file that are not frequently used

* shared virtual memory

st idea: allow processes on different machines to share virtual memory

gives the illusion of physical shared memory, across a network

st replicate pages that are only read

* invalidate copies on write

* JOS and virtual memory

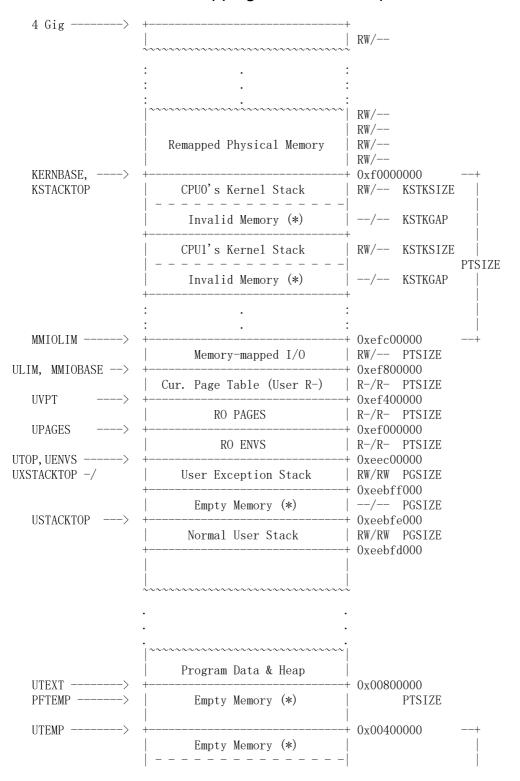

* layout: [picture] (1-josmem.html)

* UVPT trick (lab 4)

recursively map PD at 0x3BD

virtual address of PD is (0x3BD<<22) | (0x3BD<<12)

if we want to find pte for virtual page n, compute

pde_t uvpt[n], where uvpt is (0x3BD << 22)</pre>

= uvpt + n * 4 (because pdt is a word)

= (0x3BD \ll 22) | (top 10 bits of n) | (bottom 10 bits of n) \le 2

= 10 | 10 | 12

for example, uvpt[0] is address (0x3BD << 22), following the pointers gives us

the first entry in the page directory, which points to the first page table, which

we index with 0, which gives us pte 0

simpler than pgdirwalk()?

* user-level copy-on-write fork (lab4)

JOS propagates page faults to user space

user programs can play similar VM tricks as kernel!

```

you will do user-level copy-on-write fork

# How we will use paging (and segments) in JOS:

- use segments only to switch privilege level into/out of kernel

- use paging to structure process address space

- use paging to limit process memory access to its own address space

- below is the JOS virtual memory map

- why map both kernel and current process? why not 4GB for each? how does this compare with xv6?

- why is the kernel at the top?

- why map all of phys mem at the top? i.e. why multiple mappings?

- (will discuss UVPT in a moment...)

- how do we switch mappings for a different process?

#### The UVPT

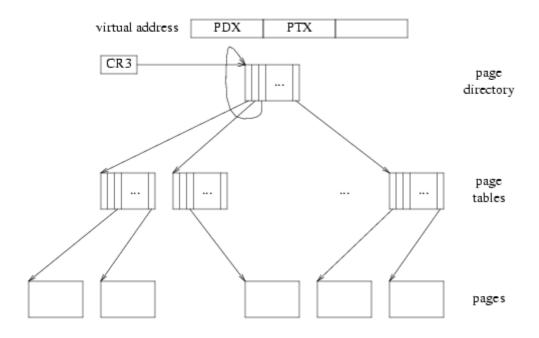

We had a nice conceptual model of the page table as a 2^20-entry array that we could index with a physical page number. The x86 2-level paging scheme broke that, by fragmenting the giant page table into many page tables and one page directory. We'd like to get the giant conceptual page-table back in some way -- processes in JOS are going to look at it to figure out what's going on in their address space. But how?

Luckily, the paging hardware is great for precisely this -- putting together a set of fragmented pages into a contiguous address space. And it turns out we already have a table with pointers to all of our fragmented page tables: it's the page directory!

So, we can use the page *directory* as a page *table* to map our conceptual giant 2^22-byte page table (represented by 1024 pages) at some contiguous 2^22-byte range in the virtual address space. And we can ensure user processes can't modify their page tables by marking the PDE entry as read-only.

Puzzle: do we need to create a separate UVPD mapping too?

A more detailed way of understanding this configuration:

Remember how the X86 translates virtual addresses into physical ones:

CR3 points at the page directory. The PDX part of the address indexes into the page directory to give you a page table. The PTX part indexes into the page table to give you a page, and then you add the low bits in.

But the processor has no concept of page directories, page tables, and pages being anything other than plain memory. So there's nothing that says a particular page in memory can't serve as two or three of these at once. The processor just follows pointers: pd = lcr3(); pt = \*(pd+4\*PDX); page = \*(pt+4\*PTX);

Diagramatically, it starts at CR3, follows three arrows, and then stops.

If we put a pointer into the page directory that points back to itself at index V, as in

then when we try to translate a virtual address with PDX and PTX equal to V, following three arrows leaves us at the page directory. So that virtual page translates to the page holding the page directory. In Jos, V is 0x3BD, so the virtual address of the UVPD is (0x3BD <<22)|(0x3BD <<12).

Now, if we try to translate a virtual address with PDX = V but an arbitrary PTX != V, then following three arrows from CR3 ends one level up from usual (instead of two as in the last case), which is to say in the page tables. So the set of virtual pages with PDX=V form a 4MB region whose page contents, as far as the processor is concerned, are the page tables themselves. In Jos, V is 0x3BD so the virtual address of the UVPT is (0x3BD < <22).

So because of the "no-op" arrow we've cleverly inserted into the page directory, we've mapped the pages being used as the page directory and page table (which are normally virtually invisible) into the virtual address space.

```

6.828 2017 Lecture 8: System calls, Interrupts, and Exceptions

Let's start with the homework

alarmtest.c

alarm(10, periodic)

asks kernel to call periodic() every 10 "ticks" in this process

that is, every 10 ticks of CPU time that this process consumes

three pieces:

add a new system call

count ticks as the program runs (timer interrupt)

kernel "upcall" to periodic()

the call to periodic() is a simplified UNIX signal

glue for a new system call

syscall.h: #define SYS alarm 22

usys. S: SYSCALL (alarm)

alarmtest.asm -- mov $0x16, %eax -- 0x16 is SYS_alarm

syscall.c syscalls[] table

sysproc.c sys_alarm()

why all this machinery?

at a high level, alarmtest just wants to make a function call to sys_alarm

it has to be indirect (via INT, SYS_alarm) to maintain isolation

break sys_alarm

where

how did syscall know which system call?

trapframe, on kernel stack, has saved user eax

print myproc()->tf->eax

where does sys alarm find the arguments, ticks and handler?

on the user stack

x/4x \text{ myproc}() - tf - esp

does the handler value make sense? look in alarmtest.asm

now we need to take some action whenever the timer h/w interrupts

decrement ticksleft

if expired

upcall to handler (periodic())

reset ticksleft

device interrupts arrive just like INT and pagefault

h/w pushes esp and eip on kernel stack

s/w saves other registers, into a trapframe

vector, alltraps, trap()

timer interrupts served by IRQ TIMER case in trap()

original IRQ TIMER task is to keep track of wall-clock time, in ticks

execute to trap without an implementation

break vector32

where

print/x tf->eip

print/x tf->esp

x/4x tf->esp

what was the user program doing at this point?

tf->eip in alarmtest.asm

user code could have been interrupted anywhere

so we can't rely on anything about the user stack

and we need to restore registers exactly, since program didn't save anything

Q: how to arrange for upcall to alarm handler?

call myproc()->alarmhandler() ?

tf->eip = myproc()->alarmhandler ?

Q: how to ensure handler returns to interrupted user code?

add our code...

run alarmtest without gdb

```

```

let's run with gdb

list trap to find breakpoint

print/x tf->eip before assignment

print/x tf→eip after assignment

break *0x74

info reg

will it return somewhere reasonable in alarmtest.asm?

x/4x \$esp

Q: what's the security problem in my new trap() code?

Q: what if trap() directly called alarmhandler()?

it's a bad idea

but what exactly would go wrong?

let's try it

it doesn't crash!

but it doesn't print alarm! either. why not?

fetchint...

apparently it gets back to user space (to print .) -- how?

program, timer trap, alarmhandler(), INT, sys_write("alarm!"), return...

stack diagram

it is disturbing how close this came to working!

why can kernel code directly jump to user instructions?

why can user instructions modify the kernel stack?

why do system calls (INT) work from the kernel?

none of these are intended properties of xv6!

the x86 h/w does *not* directly provide isolation

x86 has many separate features (page table, INT, &c)

it's possible to configure these features to enforce isolation

but isolation is not the default!

Q: what happens if just tf->eip = alarmhandler, but don't push old eip?

let's try it

user stack diagram

Q: what if trap() didn't check for CPL 3?

let's try it — seems to work!

how could tf \rightarrow cs\&3 == 0 ever arise from alarmtest?

let's force the situation with (tf->cs\&3)==0

and making alarmtest run forever

unexpected trap 14 from cpu 0 eip 801067cb (cr2=0x801050cf)

what is eip 0x801067cb in kernel.asm?

tf \rightarrow esp = tf \rightarrow eip in trap().

what happened?

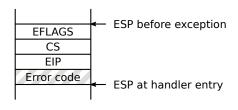

it was a CPL=0 to CPL=0 interrupt

so the h/w didn't switch stacks

so it didn't save %esp

so tf->esp contains garbage

(see comment at end of trapframe in x86.h)

the larger point is that interrupts can occur while in the kernel (in xv6, not JOS)

Q: what will happen if user-supplied alarm handler fn points into the kernel?

(with the correct trap() code)

Q: what if another timer interrupt goes off while in user handler?

works, but confusing, and will eventually run out of user stack

maybe kernel shouldn't re-start timer until handler function finishes

Q: is it a problem if periodic() modifies registers?

how could we arrange to restore registers before returning?

let's step back and talk about interrupts a bit more generally

the general topic: h/w wants attention now!

s/w must set aside current work and respond

```

```

where do traps come from?

(I use "trap" as a general term)

device -- data ready, or completed an action, ready for more

exception/fault -- page fault, divide by zero, &c

INT -- system call

IPI -- kernel CPU-to-CPU communication, e.g. to flush TLB

where do device interrupts come from?

diagram:

CPUs, LAPICs, IOAPIC, devices

data bus

interrupt bus

the interrupt tells the kernel the device hardware wants attention

the driver (in the kernel) knows how to tell the device to do things

often the interrupt handler calls the relevant driver

but other arrangements are possible (schedule a thread; poll)

how does trap() know which device interrupted?

i.e. where did tf->trapno == T IRQO + IRQ TIMER come from?

kernel tells LAPIC/IOAPIC what vector number to use, e.g. timer is vector 32

page faults &c also have vectors

LAPIC / IOAPIC are standard pieces of PC hardware

one LAPIC per CPU

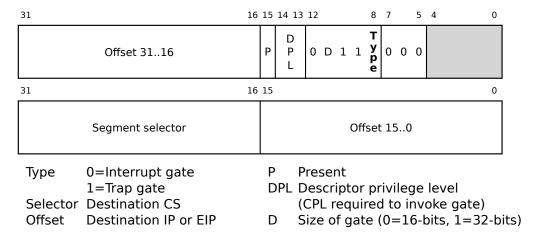

IDT associates an instruction address with each vector number

IDT format is defined by Intel, configured by kernel

each vector jumps to alltraps

CPU sends many kinds of traps through IDT

low 32 IDT entries have special fixed meaning

xv6 sets up system calls (IRQ) to use IDT entry 64 (0x40)

the point: the vector number reveals the source of the interrupt

diagram:

IRQ or trap, IDT table, vectors, alltraps

IDT:

0: divide by zero

13: general protection

14: page fault

32-255: device IRQs

32: timer

33: keyboard

46: IDE

64: INT

let's look at how xv6 sets up the interrupt vector machinery

lapic.c / lapicinit() -- tells LAPIC hardware to use vector 32 for timer

trap.c / tvinit() -- initializes IDT, so entry i points to code at vector[i]

this is mostly purely mechanical, IDT entries correspond blindly to vectors

BUT T_SYSCALL's 1 (vs 0) tells CPU to leave interrupts enabled during system calls

but not during device interrupts

Q: why allow interrupts during system calls?

Q: why disable interrupts during interrupt handling?

vectors. S (generated by vectors. pl)

first push fakes "error" slot in trapframe, since h/w doesn't push for some traps

second push is just the vector number

this shows up in trapframe as tf->trapno

how does the hardware know what stack to use for an interrupt?

when it switches from user space to the kernel

hardware-defined TSS (task state segment) lets kernel configure CPU

so each CPU can run a different process, take traps on different stacks

proc. c / scheduler()

one per CPU

vm.c / switchuvm()

tells CPU what kernel stack to use

tells kernel what page table to use

Q: what eip should the CPU save when trapping to the kernel?

eip of the instruction that was executing?

```

eip of the next instruction?

suppose the trap is a page fault?

## some design notes

- \* interrupts used to be relatively fast; now they are slow old approach: every event causes an interrupt, simple h/w, smart s/w new approach: h/w completes lots of work before interrupting

- \* an interrupt takes on the order of a microsecond save/restore state cache misses

- \* some devices generate events faster than one per microsecond e.g. gigabit ethernet can deliver 1.5 million small packets / second

- \* polling rather than interrupting, for high-rate devices if events are always waiting, no need to keep alerting the software

- \* interrupt for low-rate devices, e.g. keyboard constant polling would waste CPU

- \* switch between polling and interrupting automatically interrupt when rate is low (and polling would waste CPU cycles) poll when rate is high (and interrupting would waste CPU cycles)

- \* faster forwarding of interrupts to user space for page faults and user-handled devices h/w delivers directly to user, w/o kernel intervention? faster forwarding path through kernel?

we will be seeing many of these topics later in the course

# Interrupt/trap gate

# Exception stack (with privilege change)

# Exception stack (without privilege change)

| Vector | Description              | Туре      | Error code | Excep | tion types                         |

|--------|--------------------------|-----------|------------|-------|------------------------------------|

| 0      | Divide error             | Fault     | No         | Fault | Faulting instruction not executed  |

| 1      | Reserved                 |           |            |       | CS:EIP is the faulting instruction |

| 2      | Non-maskable interrupt   | Interrupt | No         | Trap  | Trapping instruction executed      |

| 3      | Breakpoint               | Trap      | No         |       | CS:EIP is the next instruction     |

| 4      | Overflow                 | Trap      | No         | Abort | Location is imprecise; cannot      |

| 5      | BOUND range exceeded     | Fault     | No         |       | safely resume execution            |

| 6      | Invalid/undefined opcode | Fault     | No         | 31    | 3 2 1 0                            |

| 7      | No math coprocessor      | Fault     | No         |       |                                    |

| 8      | Double fault             | Abort     | Zero       |       | Segment selector                   |

| 9      | Reserved                 |           |            |       |                                    |

| 10     | Invalid TSS              | Fault     | Yes        |       |                                    |

| 11     | Segment not present      | Fault     | Yes        | TI    | 0=GDT, 1=LDT                       |

| 12     | Stack-segment fault      | Fault     | Yes        | IDT   | 0=GDT/LDT, 1=IDT                   |

| 13     | General protection       | Fault     | Yes        | EXT   | External event                     |

| 14     | Page fault               | Fault     | Yes        | 31    | 3 2 1 0                            |

| 15     | Reserved                 |           | No         |       | u w                                |

| 16     | x87 FPU error            | Fault     | No         |       | /   /   P                          |

| 17     | Alignment check          | Fault     | Zero       |       | S R                                |

| 18     | Machine check            | Abort     | No         | Р     | 0=Non-present page                 |

| 19     | SIMD FP exception        | Fault     | No         | '     | 1=Protection-violation             |

| 20-31  | Reserved                 |           |            | W/R   | Cause (0=Read, 1=Write)            |

| 32-255 | User defined interrupts  | Interrupt | No         | U/S   | Mode (0=Supervisor, 1=User)        |

```

Why talk about locking?

apps want to use multi-core processors for parallel speed-up

so kernel must deal with parallel system calls

and thus parallel access to kernel data (buffer cache, processes, &c)

locks help with correct sharing of data

locks can limit parallel speedup

Locking homework

recall: ph.c, multi-threaded hash table, put(), get()

vi ph0.c

Q: why run ph.c on multiple cores?

diagram: CPUs, bus, RAM

assumption: CPU is bottleneck, can divide work between CPUs

Q: can we beat single-core put() time? single-core get() time?

Q: how to measure parallel speedup?

./ph0 2

twice as much work per unit time!

Q: where are the missing keys?

Q: specific scenario?

diagram...

table[0] = 15

concurrent put(5), put(10)

both insert()s allocate new entry, point next to 15

both set table[0] to their new entry

last inserter wins, other one is lost!

called a "lost update"; example of a "race"

race = concurrent accesses; at least one write

Q: where to put the lock/unlock?

Q: one lock covering the whole hash table?

why? why not?

called a "big" or "coarse-grained" lock

./ph1 2

faster? slower? why?

Q: one lock per table[] entry?

this lock is "finer grained"

why might this be good?

./ph2 2

faster? slower? why?

what might be harder with per-bucket locks?

will we get a good speedup with 10 cores? NBUCKET=5...

Q: one lock per struct entry, protecting the next pointer?

why? why not?

Q: does get() need to lock?

Q: does get() need to lock if there are concurrent put()s?

it's a race; but is it incorrect?

The lock abstraction:

lock 1

acquire(1)

x = x + 1 -- "critical section"

release(1)

a lock is itself an object

if multiple threads call acquire(1)

only one will return right away

the others will wait for release() -- "block"

a program typically has lots of data, lots of locks

if different threads use different data,

then they likely hold different locks,

so they can execute in parallel -- get more work done.

note that lock 1 is not specifically tied to data x

the programmer has a plan for the correspondence

A conservative rule to decide when you need to lock:

any time two threads use a memory location, and at least one is a write

don't touch shared data unless you hold the right lock!

```

(too strict: program logic may sometimes rule out sharing; lock-free)

```

(too loose: printf(); not always simple lock/data correspondence)

Could locking be automatic?

perhaps the language could associate a lock with every data object

compiler adds acquire/release around every use

less room for programmer to forget!

that idea is often too rigid:

rename("d1/x", "d2/y"):

lock dl, erase x, unlock dl

lock d2, add y, unlock d2

problem: the file didn't exist for a while!

rename() should be atomic

other system calls should see before, or after, not in between

otherwise too hard to write programs

we need:

lock d1; lock d2

erase x, add y

unlock d2; unlock d1

that is, programmer often needs explicit control over

the region of code during which a lock is held

in order to hide awkward intermediate states

Ways to think about what locks achieve

locks help avoid lost updates

locks help you create atomic multi-step operations -- hide intermediate states

locks help operations maintain invariants on a data structure

assume the invariants are true at start of operation

operation uses locks to hide temporary violation of invariants

operation restores invariants before releasing locks

Problem: deadlock

notice rename() held two locks

what if:

core A

core B

rename (d1/x, d2/y) rename (d2/a, d1/b)

lock d1

lock d2

lock d2 ...

lock d1 ...

solution:

programmer works out an order for all locks

all code must acquire locks in that order

i.e. predict locks, sort, acquire -- complex!

Locks versus modularity

locks make it hard to hide details inside modules

to avoid deadlock, I need to know locks acquired by functions I call

and I may need to acquire them before calling, even if I don't use them

i.e. locks are often not the private business of individual modules

How to think about where to place locks?

here's a simple plan for new code

1. write module to be correct under serial execution

i.e. assuming one CPU, one thread

insert() { e \rightarrow next = 1; 1 = e; }

but not correct if executed in parallel

2. add locks to FORCE serial execution

since acquire/release allows execution by only one CPU at a time

it's easier for programmers to reason about serial code

locks can cause your serial code to be correct despite parallelism

What about performance?

after all, we're probably locking as part of a plan to get parallel speedup

Locks and parallelism

locks *prevent* parallel execution

to get parallelism, you often need to split up data and locks

in a way that lets each core use different data and different locks

"fine grained locks"

choosing best split of data/locks is a design challenge

```

```

whole ph.c table; each table[] row; each entry

whole FS; directory/file; disk block

whole kernel; each subsystem; each object

you may need to re-design code to make it work well in parallel

example: break single free memory list into per-core free lists

helps if threads were waiting a lot on lock for single free list

such re-writes can require a lot of work!

Lock granularity advice

start with big locks, e.g. one lock protecting entire module

less deadlock since less opportunity to hold two locks

less reasoning about invariants/atomicity required

measure to see if there's a problem

big locks are often enough -- maybe little time spent in that module

re-design for fine-grained locking only if you have to

Let's look at locking in xv6.

A typical use of locks: ide.c

typical of many O/S's device driver arrangements

user processes, kernel, FS, iderw, append to disk queue

IDE disk hardware

ideintr

sources of concurrency: processes, interrupt

only one lock in ide.c: idelock -- fairly coarse-grained

iderw() -- what does idelock protect?

1. no races in idequeue operations

2. if queue not empty, IDE h/w is executing head of queue

3. no concurrent access to IDE registers

ideintr() -- interrupt handler

acquires lock -- might have to wait at interrupt level!

uses idequeue (1)

hands next queued request to IDE h/w (2)

touches IDE h/w registers (3)

How to implement locks?

why not:

struct lock { int locked; }

acquire(1) {

while(1) {

if (1-) locked == 0) \{ // A

1\rightarrowlocked = 1; // B

return;

oops: race between lines A and B

how can we do A and B atomically?

Atomic exchange instruction:

mov $1, %eax

xchg %eax, addr

does this in hardware:

lock addr globally (other cores cannot use it)

temp = *addr

*addr = %eax

%eax = temp

x86 h/w provides a notion of locking a memory location

different CPUs have had different implementations

diagram: cores, bus, RAM, lock thing

so we are really pushing the problem down to the hardware

h/w implements at granularity of cache-line or entire bus

memory lock forces concurrent xchg's to run one at a time, not interleaved

acquire(1) {

while (1) {

```

```

if (xchg(\&1->locked, 1) == 0) {

break

if 1->locked was already 1, xchg sets to 1 (again), returns 1,

and the loop continues to spin

if 1->locked was 0, at most one xchg will see the 0; it will set

it to 1 and return 0; other xchgs will return 1

this is a "spin lock", since waiting cores "spin" in acquire loop

Look at xv6 spinlock implementation